# HEWLETT-PACKARD JOURNAL

October 1993

# HEWLETT-PACKARD JOURNAL

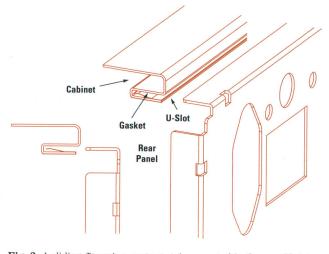

# Articles

| 6 | An 8-Gigasample-per-Second Modular Digitizing Oscilloscope System, by John A. Scharrer                                                                         |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | An 8-Gigasample-per-Second, 8-Bit Data Acquisition System for a Sampling Digital Oscilloscope, by Michael T. McTigue and Patrick J. Byrne                      |

| 1 | A Digitizing Oscilloscope Time Base and Trigger System Optimized for Throughput and Low Jitter, by David D. Eskeldson, Reginald Kellum, and Donald A. Whiteman |

|   | A Rugged 2.5-GHz Active Oscilloscope Probe, by Thomas F. Uhling and John R. Sterner                                                                            |

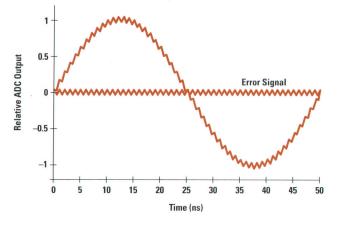

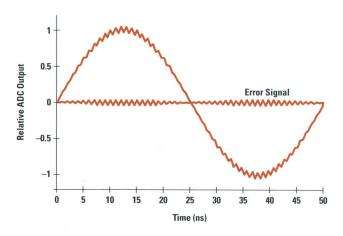

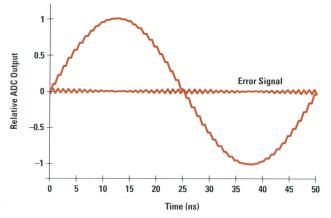

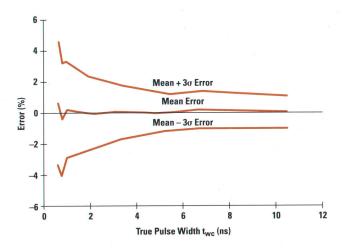

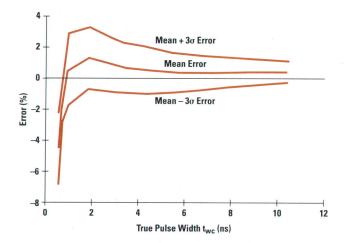

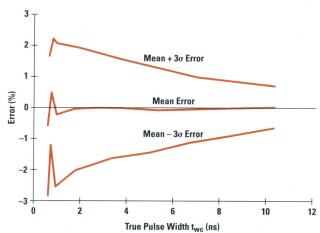

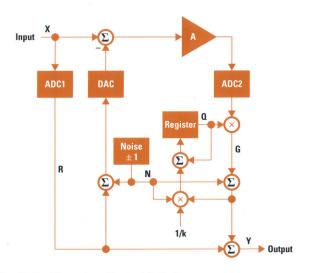

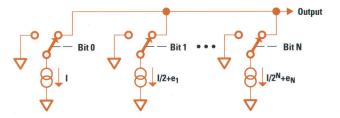

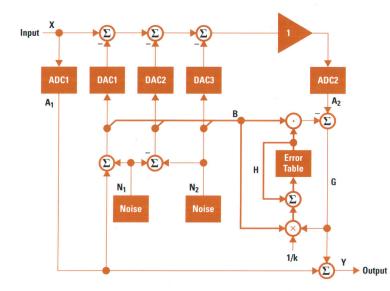

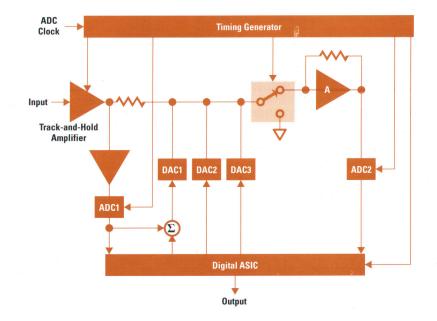

| 3 | Accuracy in Interleaved ADC Systems, by Allen Montijo and Kenneth Rush                                                                                         |

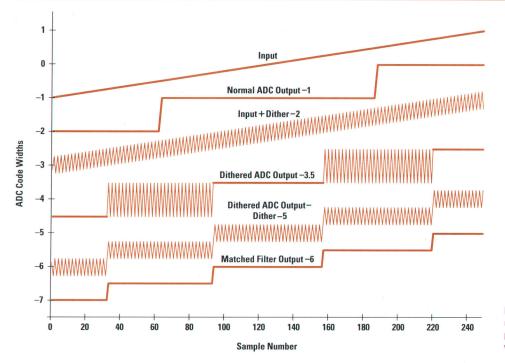

| ) | Dither and Bits                                                                                                                                                |

|   | Filter Design for Interpolation                                                                                                                                |

|   | A Study of Pulse Parameter Accuracy in Real-Time Digitizing Oscilloscope Measurements,<br>by Kenneth Rush                                                      |

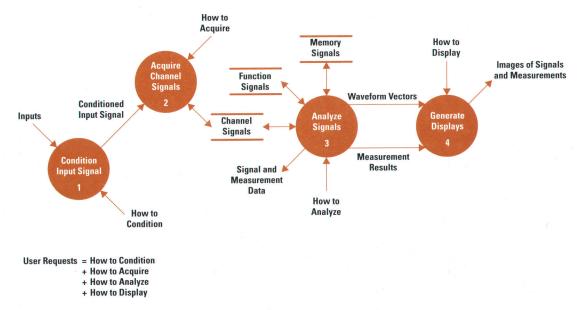

|   | Architectural Design for a Modular Oscilloscope System, by Dana L. Johnson<br>and Christopher J. Magnuson                                                      |

|   | A Survey of Processes Used in the Development of Firmware for a Multiprocessor Embedded System, by David W. Long and Christopher P. Duff                       |

|   | Developing Extensible Firmware                                                                                                                                 |

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighini Typography/Layout, Cindy Rubin • Test and Measurement Organization Liaison, Sydney C. Avey

Advisory Board, Steven Brittenham, Disk Memory Division, Boise, Idaho & William W. Brown, Integrated Circuit Business Division, Santa Clara, California • Frank J. Calvillo, Greeley Storage Division, Greeley, Colorado • Harry Chou, Microwave Technology Division, Santa Rosa, California • Derek T. Dang, System Support Division, Mountain View, California • Hajesh Desai, Commercial Systems Division, Cupertino, California • Kevin G. Evert, Integrated Systems Division, Sunnyvale, California • Bernhard Fischer, Böblingen Medrical Division, Böblingen, Germany • Douglas Gennetten, Greeley Hardoopy Division, Santa Rosa, California • Gardo • Gard Gordon, HP Laboratories, Palo Alto, California • Matt J. Harline, Systems Technology Division, Roseville, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Grace Judy, Grenoble Networks Division, Cupertino, California • Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California • Baula H. Kanarek, Inkjet Components Division, Corvaliis, Oregon • Thomas F. Kramenc, Colorado Springs Division, Colorado • Butly B. Lee, Networked Systems Group, Cupertino, California • Bill Lloyd, HP Laboratories Japan, Kawasaki, Japan • Alfred Maute, Waldbronn Analytical Division, Waldbronn, Germany • Michael P. Moore, VXI Systems Division, Loveland, Colorado • Shelley I. Moore, San Diego Printer Division, Chandsoft, Massachusetts • Steven J. Naroso, WI Systems Division, Mountain View, California • William M. Movson, Open Systems Software Division, Chelmschot, Massachusetts • Steven S I Astroso, WI Systems Division, Loveland, Colorado • Garry Orsolini, Software Technology Division, Roseville, California • Baj Oza, Software Technology Division, Mountain View, California • Han Tian Phua, Asia Peripherals Division, Singapore • Ken Poulton, HP Laboratories, Plao Atto, California • Binter Ribesell, Böldingen, Instruments Division, Corean of Near Stateella. Software Engineering Systems Division, Fort Collins, Colorado • Wichele B. Saunders , Integrated Circuit Bus

©Hewlett-Packard Company 1993 Printed in U.S.A.

F

F し

The Hewlett-Packard Journal is printed on recycled paper.

October 1993 Volume 44 • Number 5

# Departments

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 113 Authors

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1993 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304 U.S.A.

### In this Issue

Most laboratory oscilloscopes today are sampling digitizing oscilloscopes. Analog scopes simply can't match their precision and their storage and measurement capabilities. When you begin to look at digitizing oscilloscopes, the first thing you notice is that there are a lot of different kinds. For example, you can find bandwidth specifications from 100 megahertz all the way to 50 gigahertz and beyond. Going a little farther, you find that there are two kinds of bandwidth: one for capturing single-shot phenomena and one for capturing repetitive signals. Ignoring the input amplifier and sampler bandwidths for the moment, the most important bandwidth-determining parameter for single-shot events is the sampling rate—the faster the better. For repetitive signals, it's the equivalent

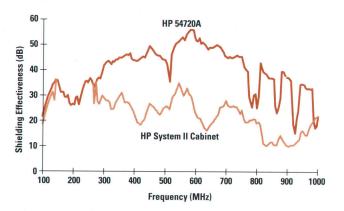

sampling rate, which depends more on the scope's timing precision than on the actual real-time sampling rate. HP designers like to use a rule of thumb that says that the potential bandwidth of the oscilloscope is one fourth of the sampling rate, either real-time or equivalent, as the case may be. The reason there are so many bandwidths to choose from is that different oscilloscopes are optimized for the needs of different applications. (The scope that does everything would be so expensive that no one would buy it.) The HP 54720A/D digitizing oscilloscope, introduced in the article on page 6, is designed to be the fastest for capturing single-shot or infrequent events such as glitches, transients, bit errors, ground bounce, and timing errors in computers and communications systems, high-energy physics phenomena, electrostatic discharge, and laser pulses. Depending on how the user configures it (there are four plug-in slots), it can have a single input channel with a sampling rate of 8 gigahertz, or two, four, or eight channels with sampling rates of four, two, or two gigahertz, respectively. A smaller sibling, the HP 54710A/D, has two plug-in slots and a maximum sampling rate of 4 GHz. For repetitive signals, a precision time base and a new trigger interpolator give the HP 54720/10 an equivalent sampling rate of 1000 GHz! However, the plug-in and sampler bandwidths limit the maximum overall bandwidth to 2 GHz. The plugins and the data acquisition system, which features four time-interleaved analog-to-digital converter acquisition hybrid circuits and a new sample-and-filter technique, are described in the article on page 11. Accuracy issues in this interleaved system are discussed on page 38. The article on page 24 gives details of the time base and trigger system. Other aspects of the design of this oscilloscope family presented in this issue are the architectural design (page 51), the mechanical design (page 66), firmware development processes (page 59), a rugged 2.5-GHz active probe (page 31), and a probe fixture for testing the acquisition hybrid (page 73). The article on page 47 reports on a study of the pulse parameter measurement accuracy of the HP 54720A only recently made possible by the availability of a wellcharacterized 50-GHz oscilloscope as a standard.

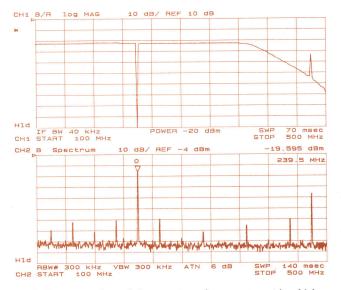

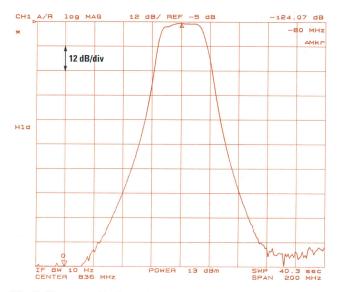

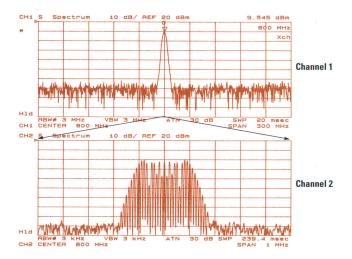

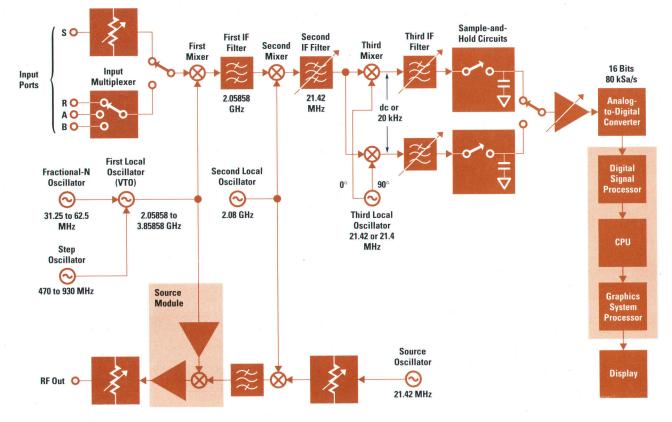

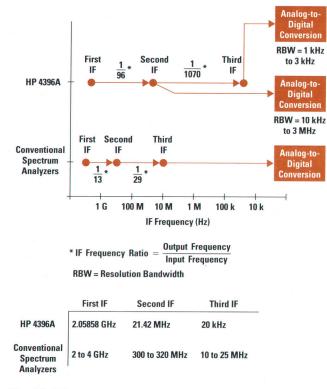

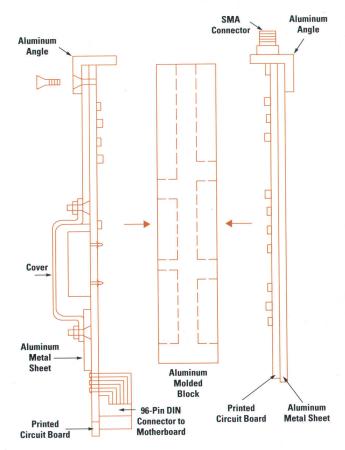

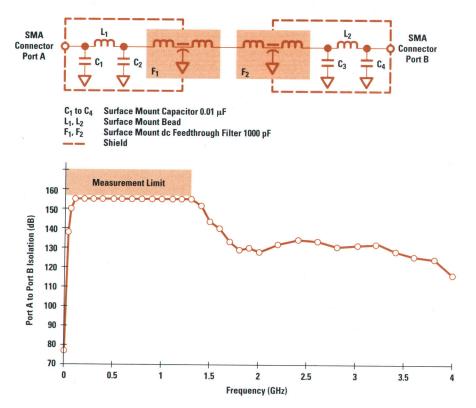

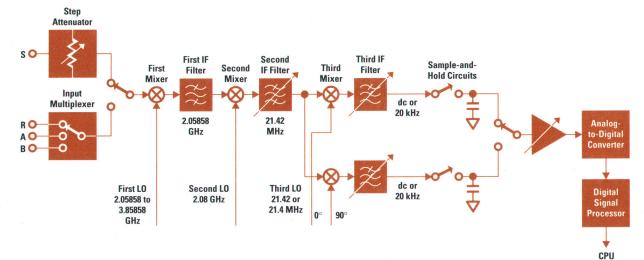

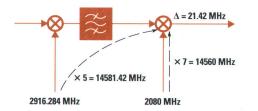

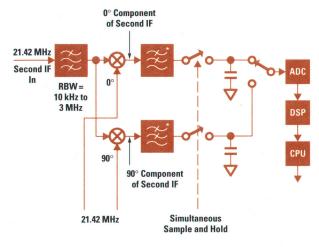

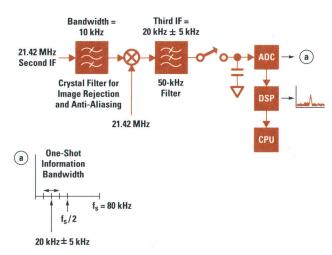

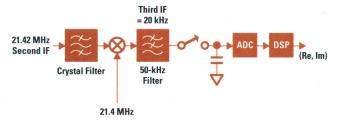

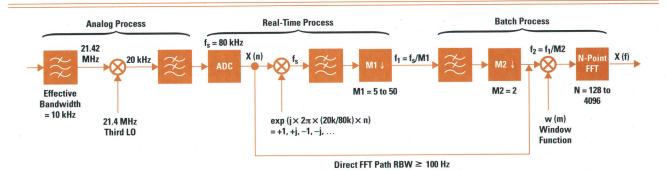

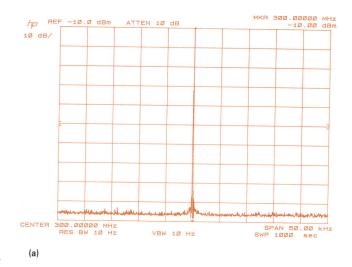

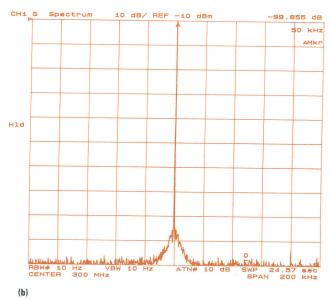

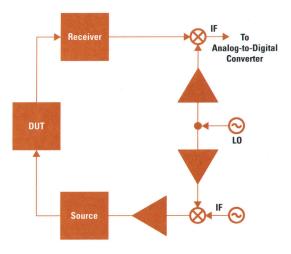

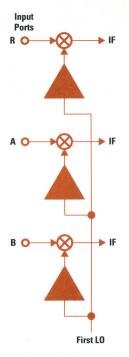

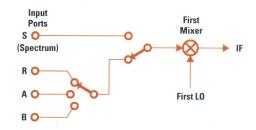

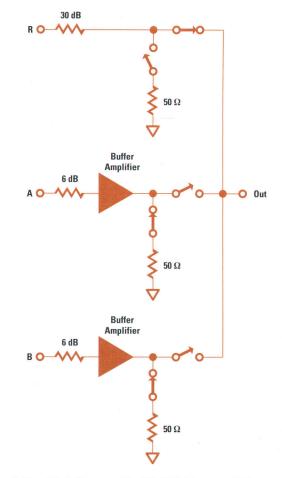

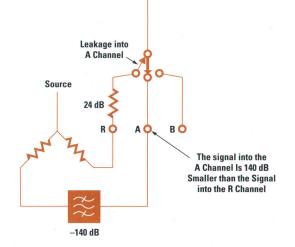

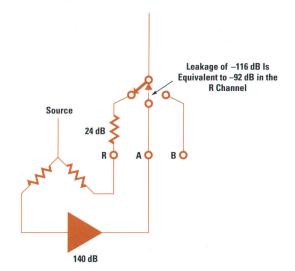

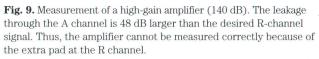

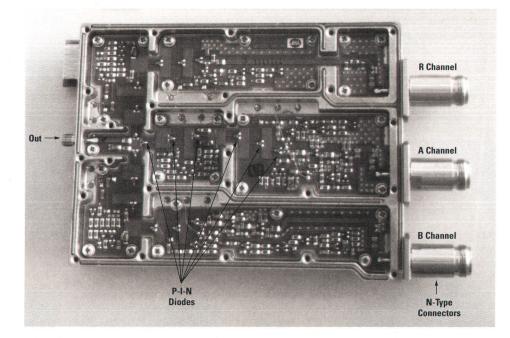

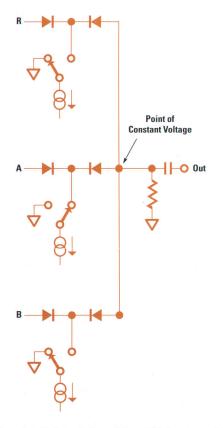

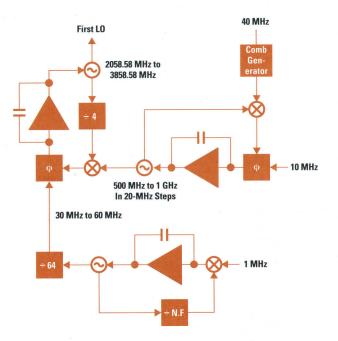

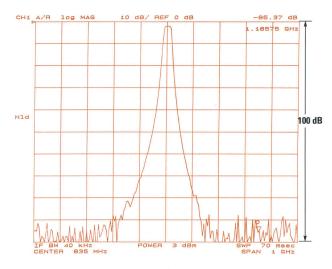

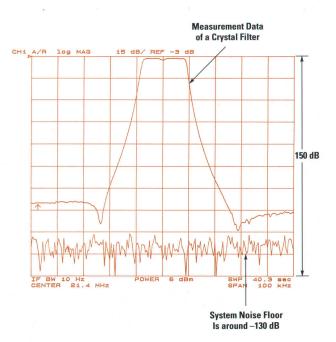

A network analyzer measures the characteristics of components or networks as functions of frequency. A spectrum analyzer measures the power in a signal as a function of frequency. Because the two are frequently used together and share some functions, a combined network and spectrum analyzer makes sense. The HP 4396A network and spectrum analyzer (page 76) is designed to offer the capabilities of both instruments without compromising the performance of either, at a lower cost than two separate instruments. The HP 4396A accepts input signals up to 1.8 gigahertz. It has two measurement display channels and can display two spectrum measurements or one network and one spectrum measurement or two network measurements at once. It has the network analyzer's usual A, B, and reference input ports, and right beside them a spectrum analyzer input port. But behind the front panel, all of these inputs go to the same measurement receiver, thereby reducing the cost considerably. To make this possible, a fast-switching, high-isolation multiplexer connects the input ports to the receiver one at a time. The receiver design is described in the article on page 85 and the multiplexer design on page 95. A nice feature is the spectrum monitor mode of the network analyzer ports, which allows the user to get a rough idea of the spectrum of a signal without disconnecting it and reconnecting it to the spectrum analyzer port.

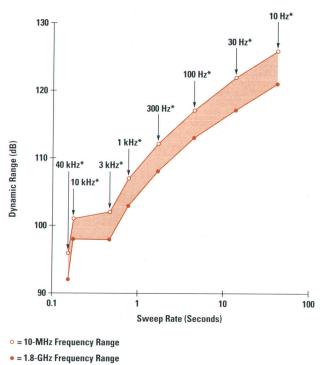

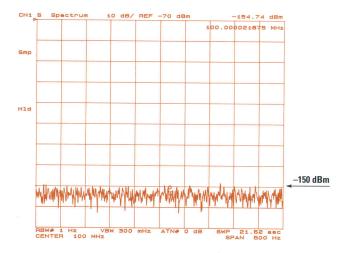

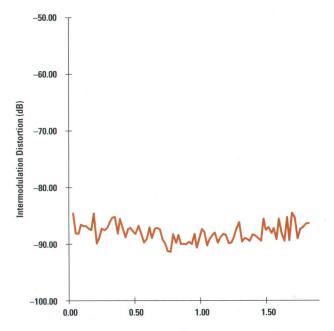

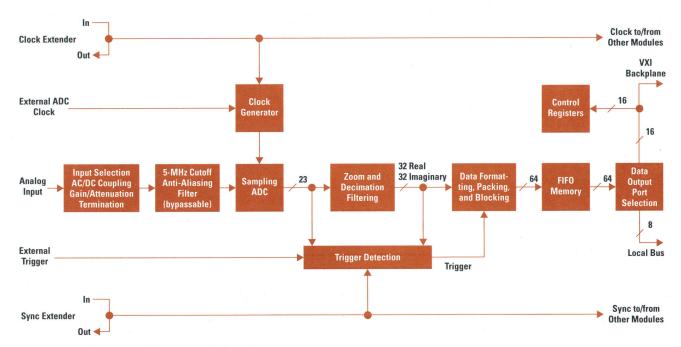

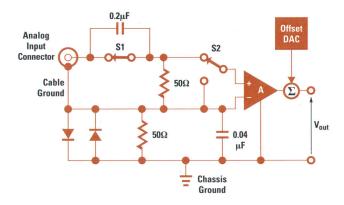

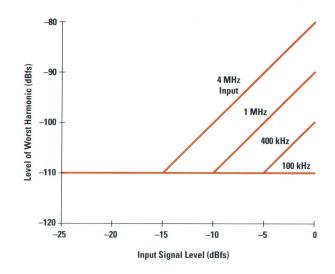

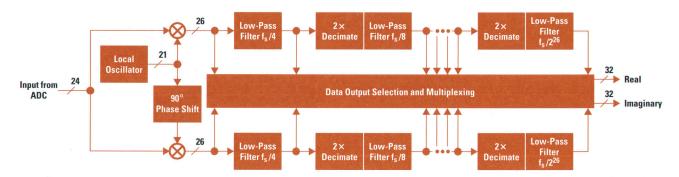

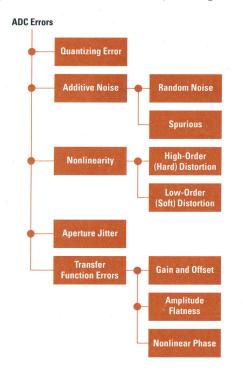

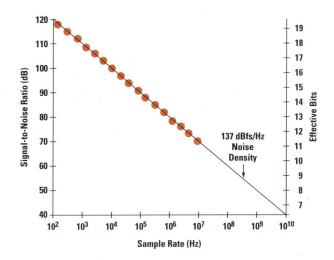

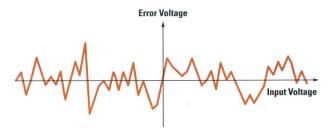

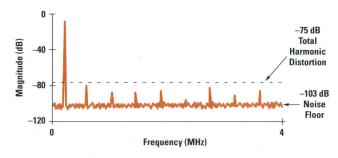

An essential component of any computer-based data acquisition or measurement system is the analogto-digital converter, or ADC, which converts analog voltages representing real-world phenomena to digital data that can be manipulated by a computer. The basic trade-off in the design of an ADC is conversion rate—the number of samples per second that can be converted—versus the precision with which each sample is converted: a higher conversion rate costs something in precision. The HP E1430A (page 100) is an ADC module designed for instrumentation systems based on the modular VXIbus standard. It includes a ten-megasample-per-second ADC and circuitry for amplitude range switching, filtering, frequency band selection, triggering, data buffering (memory), and multichannel synchronization. While its conversion rate is considerably slower than the two-gigasample-per-second ADC hybrids with which it shares this issue, its precision is much greater. Its precision, in terms of noise, distortion, and nonlinearities (or the relative lack of these defects), is quantified in the article on page 105.

> R.P. Dolan Editor

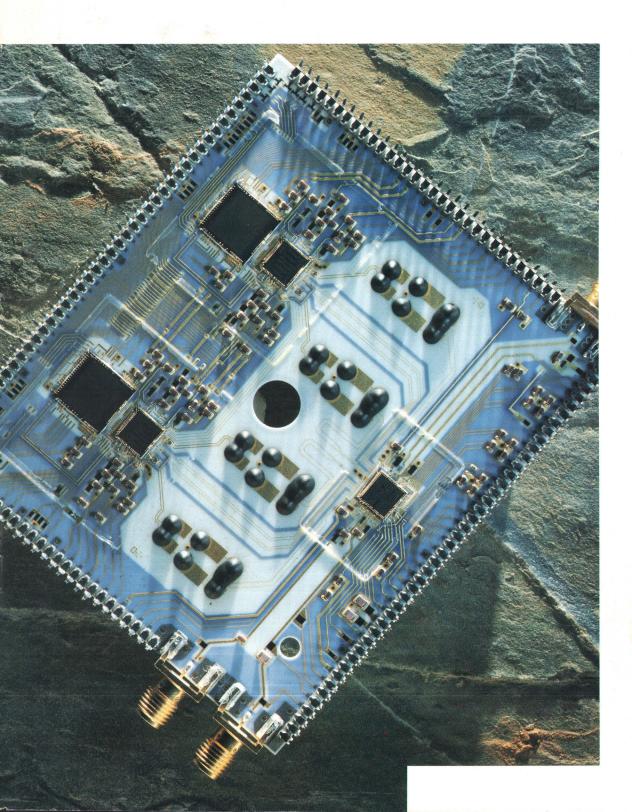

#### Cover

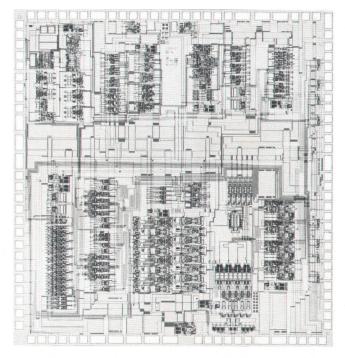

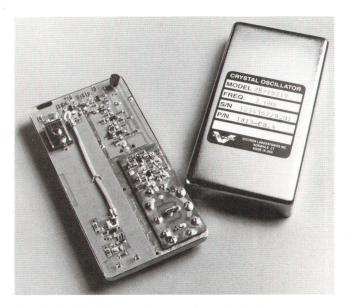

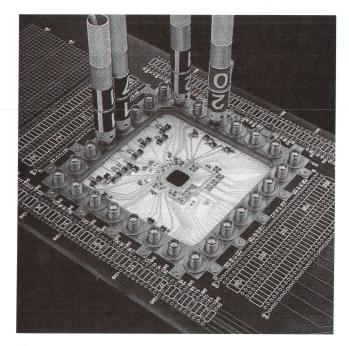

This is the acquisition hybrid microcircuit of the HP 54720D and HP 54710D oscilloscopes. There are four of these four-channel hybrids in each instrument. This circuit differs slightly from the acquisition hybrid shown in Fig. 5 on page 14, which is from the HP 54720A and HP 54710A oscilloscopes. Both hybrids have the same function and the same 2-GHz sample rate, but the D version has bigger sample memory chips and a different filter layout.

### What's Ahead

The December issue will feature the HP 89410A and 89440A vector signal analyzers, which are designed to measure the magnitude and phase of time-varying and complex modulated signals. In addition to conventional spectrum analysis, they offer a full set of measurements based on digital signal processing. Also in this issue will be the design story of the HP 71450A and 71451A optical spectrum analyzers, an article on North American cellular CDMA (code division multiple access), which is a system for packing more cellular phone users into the available frequency spectrum, an article on HP spectrum analyzer measurement capabilities for testing to the Digital European Cordless Telecommunications (DECT) standard, and an article on a standard data format used by many HP instruments for data interchange.

# An 8-Gigasample-per-Second Modular Digitizing Oscilloscope System

For the first time, a digitizing sampling oscilloscope achieves single-shot bandwidths exceeding even the fastest laboratory analog oscilloscopes. The HP 54720/10 oscilloscope combines a 2-GSa/s digitizer, plug-in modularity, and software flexibility to provide the application-specific and general-purpose capabilities needed by designers of high-speed digital devices and systems.

#### by John A. Scharrer

The need to observe low-duty-cycle or single-shot electrical waveforms has been with us for a long time. This need has been greatly intensified with the advent of high-speed digital computer and digital communication circuits and systems. These high-speed systems are prone to glitches, ground bounce, and timing problems. These problems are usually the result of complex algorithmic processes which by their very nature result in rarely occurring problems that are hard to find and observe, but critical.

Schemes to observe fast single-shot signals have been analog in nature and generally involve storing electron beam traces on a phosphor target in a conventional cathode ray tube. If the phosphor has a fast writing rate and long enough persistence, the image can be photographed with high-speed film. Storage-tube CRT technology allows direct visual observation of the waveforms without a camera. There have been many variations on this theme, but improvements in performance have been very limited in recent years and significant disadvantages to this approach are difficult if not impossible to overcome. Among these are trace blooming, dim traces, CRT wearout, displays burned permanently into the phosphor, and small displays.

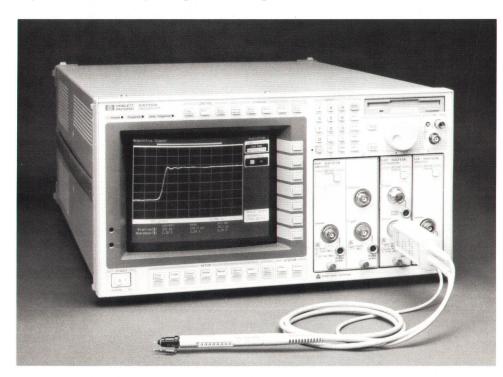

Until recently this approach was the only hope of achieving high-bandwidth single-shot capability. Now, with the introduction of the HP 54720 and 54710 digitizing oscilloscope mainframes, performance exceeding that of analog storage oscilloscopes is available. The HP 54720 (Fig. 1) and 54710 use a new high-speed digitizer methodology coupled with major improvements in computing, display technology, and product design to achieve this performance.

The HP 54720/10 system is modular. The HP 54720 mainframe provides four digitizing input slots, which accept plug-ins that offer bandwidths from 500 MHz to 2 GHz, sensitivities

**Fig. 1.** The HP 54720A is a fourchannel, modular digitizing oscilloscope capable of sample rates up to 8 GSa/s. It is shown here with the HP 54701A active probe. from 2 mV/div, and input impedances of 50 ohms and 1 megohm, depending on the plug-ins selected. Each plug-in slot is matched with a 2-GSa/s (gigasample per second) analog-todigital converter system, and by choosing a 2-slot-wide or a 4-slot-wide plug-in, sample rates of 4 GSa/s and 8 GSa/s are achieved. The HP 54710 mainframe provides two input slots. The HP 54720D and 54710D mainframes have memory depths of 64K samples per slot, and with 2-slot-wide or 4-slot-wide plug-ins, memory depth extends to 128K and 256K samples, respectively. The HP 54720A and 54710A versions of the mainframes have one quarter of the mainframe memory of the D versions.

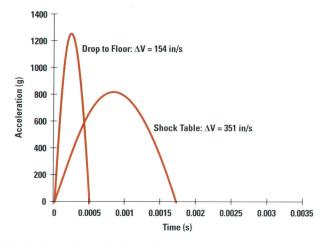

Consistent with this performance, an active probe, the HP 54701A, provides 0.5-pF input capacitance and 100-kilohm input impedance while maintaining the bandwidth of the entire system including the probe as high as 1.3 GHz depending on the plug-in selected. The probe itself has a bandwidth of greater than 2.5 GHz and can be powered either from a plug-in or from an external supply. In the past users have been reluctant to use active probes because of their mechanical fragility and the special precautions required to avoid overvoltage at the input. The HP 54701A does not require such precautions because it is protected from damage resulting from static discharge and overvoltage. In addition, it is mechanically rugged, has replaceable tips, and is highly resistant to physical damage.

Important as it is that digital storage oscilloscopes overcome the problems of analog storage, there are far more compelling reasons to move to digital storage technology. Among these are:

- The ability to store and retrieve waveforms for further analysis or for visual observation either in the oscilloscope or other environments such as a workstation

- The ability to observe pretrigger events

- Ease of use.

In addition, the HP 54720/10 project focused on providing accuracy and precision in high-bandwidth time-domain measurements and the flexibility to configure the product in software and hardware so that specific customer application needs can be supported.

#### **Storage and Pretrigger**

The HP 54720/10 acquires waveform data in digital form and stores it in memory. The waveform can be observed, scrolled, and zoomed. Cursors can be used for automatic readout and automatic measurements can be performed on the stored data. Waveform data can be routed to internal waveform memory, to an internal flexible disk drive, or to an external computer or peripheral. Digital bus interfaces provided for this purpose include the HP-IB (IEEE 488, IEC 625), Centronix, and a parallel expansion port for very high-speed data transfer.

The HP-IB port achieves data transfer rates greater than 500 kilobytes per second. Waveforms can also be transferred by flexible disk and are formatted for use by other widely used programs including spreadsheets and graphics programs.

The analog-to-digital and memory systems run continuously. When a trigger occurs, all data in memory is stored. Therefore, data occurring before the trigger (negative time) is

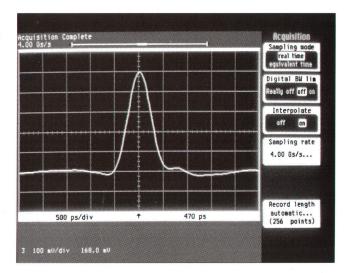

Fig. 2. The HP 54720/10 faithfully reproduces a 500-ps-wide singleshot event.

captured. This greatly facilitates troubleshooting and characterizing a system because trigger points before the point of interest are not necessary.

Of greater significance is the single-shot capability, which allows prefault observation of waveform data even if the event occurs only once. In the single-shot mode (also called the real-time mode), resolution and faithful waveform representation are determined by the analog-to-digital sample rate.

According to the Nyquist criterion, if the sample rate is twice the highest-frequency component of the signal sampled, then the signal can be faithfully reproduced. In reality, the bandwidth of an oscilloscope is down only 3 dB at the specified bandwidth and frequency components beyond the bandwidth will be sampled, causing aliasing and incorrect waveform display. To avoid this situation, Hewlett-Packard uses a rule of 4 times the specified bandwidth for the sample rate required. The HP 54720/10 achieves sample rates of 2, 4, and 8 GSa/S depending on the plug-ins selected, allowing faithful waveform reproduction at 500 MHz, 1 GHz, and 2 GHz bandwidths, respectively (Fig. 2). The maximum available sample rate is traded off against the number of channels available: 2 GSa/s allows 4 channels, 4 GSa/s allows 2 channels, and 8 GSa/s allows 1 channel.

If the signal viewed is repetitive, the equivalent time mode allows the effective sample period to be as small as one picosecond. This is achieved by accurately relating the time from the trigger event to the samples in the capture memory. After each trigger and acquisition, samples are positioned in the waveform record (and onscreen) to build up a highresolution picture of the waveform. For repetitive waveforms, equivalent time sampling can be used and the Nyquist sample rate is not an issue, but the digitizer sample rate does directly effect the throughput to the display. Using this technique for repetitive signals with the appropriate plug-ins, four channels can be observed at 2-GHz bandwidth. Using the HP 54714A dual-channel plug-in, eight channels can be viewed at 400-MHz bandwidth for repetitive signals.

#### Ease of Use and Flexibility

An oscilloscope with the advanced measurement capability of the HP 54720/10 is often referred to as a laboratory oscilloscope or a high-performance oscilloscope. The use model is focused on troubleshooting and characterizing high-speed digital systems generally in the laboratory or the preproduction phase of product development. In production this class of instrument is usually used within a system in an automated way. Focus groups of users falling into these classes were used early in the project and results of this exercise indicated the need for familiar controls, high system and display throughput, and application flexibility. These requirements dictated the system architecture and user interface.

The user interface is leveraged from the HP 541xx family of high-performance oscilloscopes with significant improvements derived from user interface studies conducted on the HP 541xx family, the general-purpose HP 545xx family, and competitive products. The resulting interface uses a pop-up menu scheme with very limited depth of menus, an intuitive graphical user interface, and extensive color. Access to often-used measurements is from the front panel instead of being buried in menus or softkey levels. The setup keys such as time base, trigger, and vertical channels are fixed and always available, rather than using softkeys and hidden levels of additional keys.

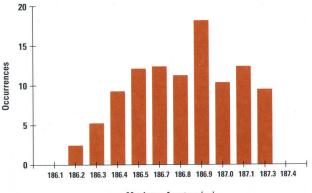

Historically, ease of use in digitizing oscilloscopes has been enhanced through the use of extensive automatic pulse parameter measurements and functions such as rise time, delay, and pulse width, to name a few. The list is ever growing and the ability to add features is very powerful in extending the value of the initial investment in the product. The fast Fourier transform (FFT), mask testing, histograms, and applications such as communications and computer design were all added after the HP 54720/10 was introduced. To accommodate this flexibility the software in the HP 54720/10 is stored in flash EPROM and SRAM and can be loaded from a flexible disk. Add-on labels and shift keys allow upgrades to be made easily, yet the added features have the same direct access as existing features. The mechanical modularity provided by plug-ins allows flexibility in configuring the inputs to the digitizers and makes it easy to customize systems for specific applications.

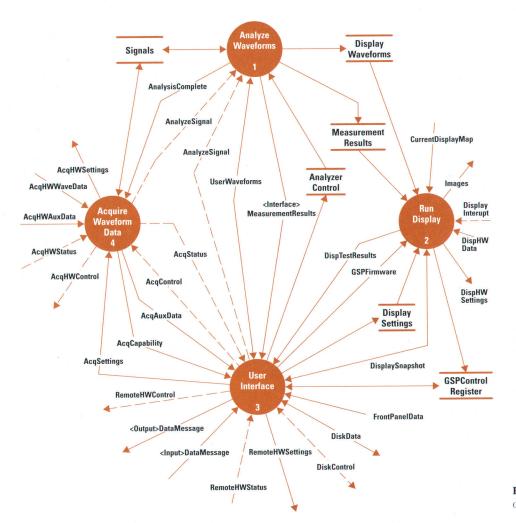

Ease-of-use studies indicate that the responsiveness of the oscilloscope to controls and signal changes is crucial to interpreting data, adjusting the device under test, and promoting confidence in the representation of viewed signals. The HP 54720/10's high waveform display rate helps avoid visual aliasing and misinterpretation of the waveforms. To achieve a high display rate, a three-processor architecture was chosen for the HP 54720/10. A CPU controls acquisition hardware and communications, performs automatic measurements, and manages waveform data, while a graphics processor and a custom display processor present the waveform data.

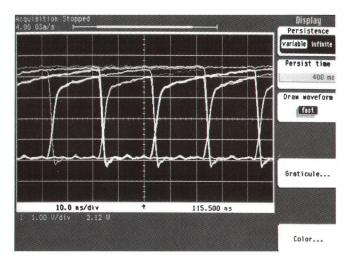

The ability not only to see changes as they occur but also to observe the relative frequency and "freshness" of data was a contribution of the HP variable-persistence analog storage oscilloscopes. With this feature, old data gradually fades away while new, brighter data is written onscreen. Until the HP 54720/10 this feature eluded digitizing oscilloscopes, but

Fig. 3. Variable persistence provides a dynamic picture of waveform changes.

the custom display processor in the HP 54720/10 accommodates this feature while maintaining a high display throughput (Fig. 3).

#### Accuracy

Although its very high digitizing sample rates and bandwidths open the door to high precision and accuracy in voltage and time measurements over a broad band of frequencies, considerable care had to be exercised in the HP 54720/10 system design to ensure that these benefits were realized. All adjustments for gain, offset, timing, and frequency response are computer-controlled (no manual adjustments) and the necessary calibration routines are automated and use calibration resources resident in the mainframe and plug-ins. Therefore the user has a self-contained accuracy calibration system. If plug-ins and mainframes are intermixed after each has been calibrated, 3% vertical gain accuracy is achieved. If a system best-accuracy calibration is performed, 1% vertical gain accuracy is achieved.

The HP 54720/10 exhibits very low jitter on repetitive singleshot or equivalent time waveform displays because of a new trigger interpolator system. The resolution of the interpolator is 1 ps and jitter on repetitive waveforms is less than 6 ps rms. Again, the internal calibration capability ensures  $\pm$ 30-picosecond time interval accuracy in equivalent time mode and  $\pm$ 50-picosecond accuracy in single-shot mode at a sample rate of 4 GSa/s.

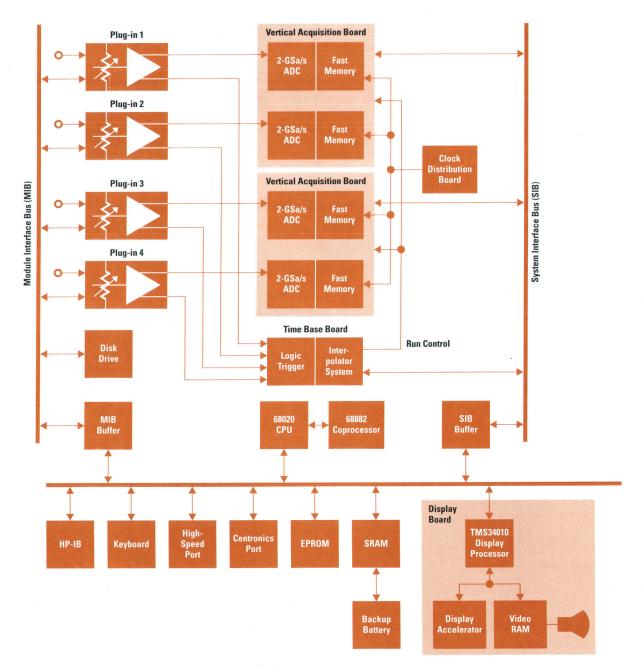

#### **System Design**

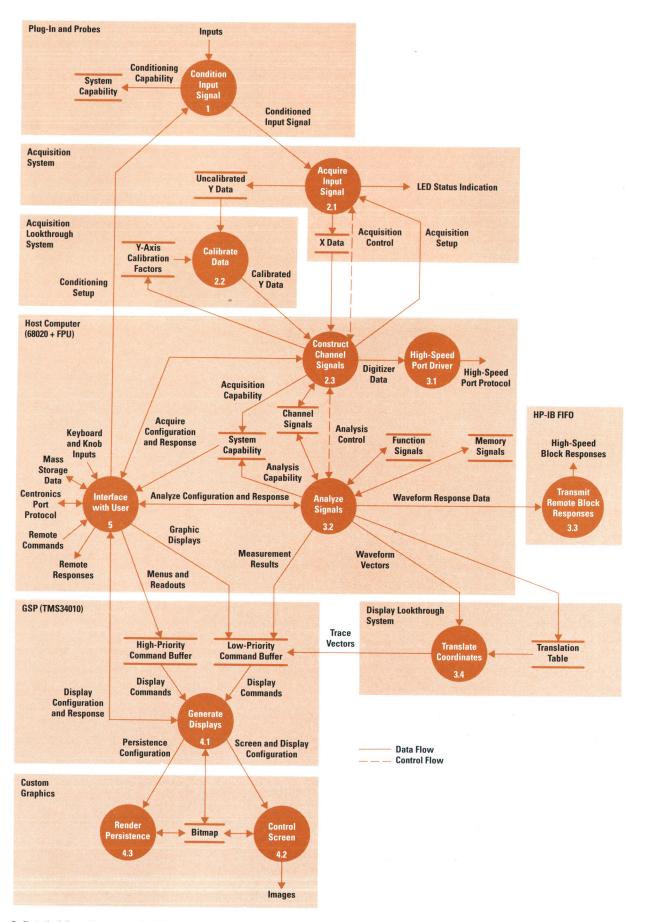

The HP 54720/10 is a flexible system whose characteristics are defined by the plug-in modules and software installed and the software features selected. A block diagram is shown in Fig. 4.

The boards in the main card cage are interconnected by the system interface bus, which carries address, data, control, and power. The plug-in modules are connected to the system via the module interface bus, which carries address, data, control, interrupts, and power.

Fig. 4. Simplified block diagram of the HP 54720/10 modular oscilloscope mainframe.

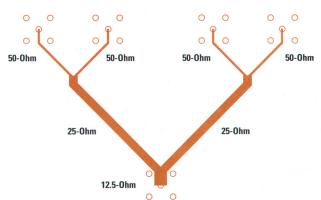

**Plug-ins.** The plug-ins determine gain, bandwidth, maximum sample rate, and input characteristics. Their general design includes an input attenuator and overvoltage protection followed by a preamplifier which also supplies a signal split for internal trigger pickoff. In the 2-slot-wide plug-in the signal is split to drive two analog-to-digital converter inputs. This split allows interleaving two analog-to-digital converters to achieve a 4 GSa/s sample rate on two channels. A passive four-way splitter in the HP 54722A 4-slot-wide plug-in achieves 8 GSa/s on one channel. The plug-ins also provide probe power and offset voltage for the HP 54701A active probe. The plug-ins are calibrated using the mainframe calibration resources and software, and the calibration factors are stored in the plug-in.

**Acquisition System.** The main and trigger signals are coupled to the mainframe through very high-bandwidth connectors and are subsequently routed to the analog-to-digital hybrid

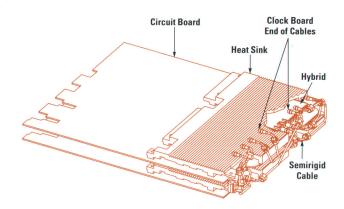

circuit and the trigger system via semirigid coaxial cable. The analog-to-digital converter hybrid uses a new technique called sample-and-filter, as opposed to sample-and-hold. The sample-and-filter technique is described in the article on page 11.

There are five monolithic integrated circuit chips on the analog-to-digital converter hybrid: a sampler and two analogto-digital converters are custom HP bipolar chips, and two fast in, slow out (FISO) memories are custom HP CMOS. The analog-to-digital subsystem including very fine-line-geometry filters are constructed on a custom Hewlett-Packard thickfilm multichip module. There are two analog-to-digital hybrids on each of the vertical acquisition boards.

The trigger signals from all four slots are input to a custom logic trigger chipset, which provides numerous combinational and sequential logic trigger capabilities. The resultant trigger is applied to an interpolator counter system, which determines the exact location of the input signal in relation to the trigger event. The waveform captured can consist of one full acquisition memory before the trigger or can be delayed up to one second after the trigger. A dual-ramp interpolator system resolves trigger location within 1 ps. The interpolation takes only six microseconds.

A clock distribution board generates a 2-GHz clock and a phase-related 100-MHz clock signal for each acquisition hybrid. The phase-related 100-MHz clock is also distributed to the time base system.

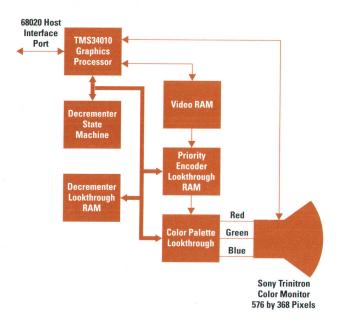

**Computer and Display.** The main system CPU is a 68020 with a 68882 floating-point coprocessor, but with an unusual feature. A state machine controls data flow on the CPU bus such that a complete 16-bit data word representing a captured sample can be moved from the FISO memory to CPU memory on each bus cycle by direct memory access (DMA). Similarly, data can be moved by DMA to the display processor and external ports. Coupled with the high-speed graphics subsystem this gives the HP 54720/10 a high-throughput, highly interactive display.

The display processor is a TMS34010 coupled to a custom HP display accelerator. The accelerator does the work of decrementing pixel brightness in variable-persistence mode, erasing the screen, and drawing lines.

The CPU RAM is nonvolatile battery-backed SRAM and the operating code is stored in flash EPROM. This allows completely changing or adding to the operating software using the flexible disk. The state of the entire oscilloscope, including all data, is preserved when the instrument is turned off.

Digital interfaces to the HP 54720/10 include the HP-IB, a Centronix printer port, and a high-speed parallel port which provides direct access to the CPU bus. The two other internal buses—the module interface bus and the system interface bus—interface with the plug-in modules and the internal system boards, respectively.

#### Software

The software system was a start-from-scratch design, and the size of the task led the design team to consider and use structured design techniques. Indeed, the first half of the software design portion of the project was design, not coding. The resulting design has been very low in defects, and adding recent features such as histograms, FFT capability, and application-specific programs went smoothly and took significantly less time than in less structured designs.

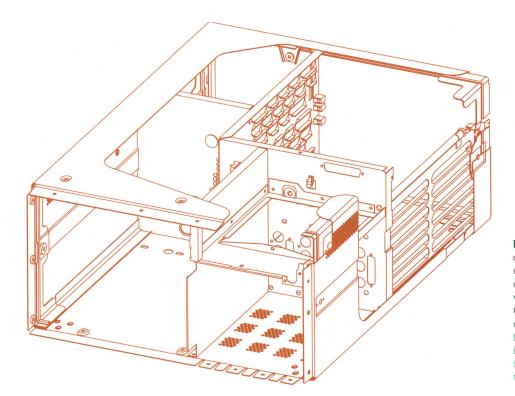

#### **Product Design**

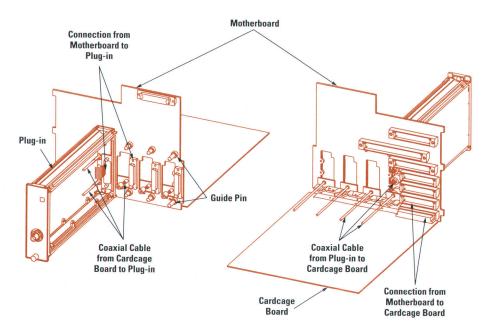

The constraints of plug-in flexibility and high-bandwidth performance led to a new modular mechanical design that makes it possible to plug high-bandwidth amplifiers into a mating mainframe with little or no signal degradation. Plug-in modularity from the front is complemented by card modularity in the rear of the mainframe. The HP 54720/10 package is the same physical size as the previous HP 541xx high-performance digitizing oscilloscopes.

#### Manufacturing

Formal concurrent engineering may require elaborate discipline and tools. The simpler concept of developing manufacturing test tools concurrently with the system and circuit design not only sufficed for this project but was indispensable in achieving the project goals. There are four analog-to-digital multichip modules per HP 54720/10 acquisition system and therefore a high loaded-hybrid yield is imperative. The hybrid test system was developed in parallel with the hybrid and ensures close to 100% loaded hybrid yield. The test system was ready in time to help develop and evaluate early prototypes. Similarly, plug-in and board test tools were defined at project inception and developed concurrently with the HP 54720/10 circuits.

#### Acknowledgments

A project of this size had a large number of contributors and they are acknowledged in the accompanying articles. In addition, recognition must go to the original concept definition team and management staff consisting of Lynne Camp, Bill Escovitz, Mike Karin, Dave Long, Fred Rampey, Ken Rush, and John Wilson. The manufacturing engineering and process team consisted of Mike Manley, Mike Van Grouw, Van Martin, Angus Foster, Jerry Townsend, Mike Kinney, Pat Ciuba, and Don Hanlon.

# An 8-Gigasample-per-Second, 8-Bit Data Acquisition System for a Sampling Digital Oscilloscope

Within the HP 54720/10 acquisition system are sixteen separate sampling and digitizing paths that can be allocated by the user to capture 16K samples at 8 GSa/s or 256K samples at 500 MSa/s or any of various other combinations of sample rate and memory depth. The sample-and-filter sampling technique is an alternative to the conventional sample-and-hold and track-and-hold techniques.

#### by Michael T. McTigue and Patrick J. Byrne

The data acquisition hardware for the HP 54720 and 54710 sampling digitizing oscilloscopes is designed to provide flexible and configurable signal capture hardware that can be tailored for different customers' needs. Variable-width plug-in amplifiers are used for signal conditioning, buffering, and splitting. The plug-ins deliver the conditioned input signals to the acquisition system, which has a sample-and-filter architecture for improved sample rate and noise performance and a scalable analog-to-digital converter (ADC) architecture that allows input channels to be traded for higher sample rates. The plug-ins support active probing to provide nonintrusive, high-bandwidth connections to the circuit under test.

### **Plug-ins**

The plug-in architecture was decided upon to meet the HP 54720/10 system design goals of configurable signal conditioning and variable signal routing. The function of a plug-in in this system is to accept the input signal to the oscilloscope, provide signal conditioning (termination impedance, ac or dc coupling, and filtering), and then present a properly scaled version of the signal to the acquisition and trigger systems in the mainframe. Plug-ins also provide support and control via a connector on the front panel for active probes and other accessories that may be needed in front of the plug-in to allow interception of a signal.

The plug-in concept provides for variable signal routing by allowing multiple-width plug-ins. The HP 54720 mainframe has four ADC channels and four trigger channels that are connected to four plug-in slots. With plug-ins that are two slots wide or four slots wide, the input signal can be fed to more than one ADC so that interleaving can be done in the mainframe and higher sampling rates can be provided.

Plug-ins protect the oscilloscope's inputs from ESD (electrostatic discharge) and excessive signal levels, and store calibration factors that reflect their own accuracies so that when they are plugged into any mainframe there is a specified level of accuracy. The intent of the input protection is that ESD or overvoltage will cause no damage to any part of the oscilloscope. In practice, and especially with high-frequency circuits, it is not always possible to protect the input from all types of overstress. Specifically, it is the plug-ins' job to protect the ADCs and trigger circuits in the mainframe from any damage. If a plug-in is damaged by excessive stress the cost to the customer is moderate, but if the ADC or trigger inputs in the mainframe are damaged, the cost to the customer could be substantial.

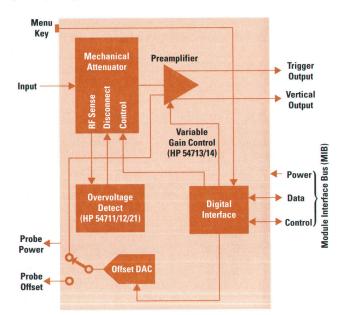

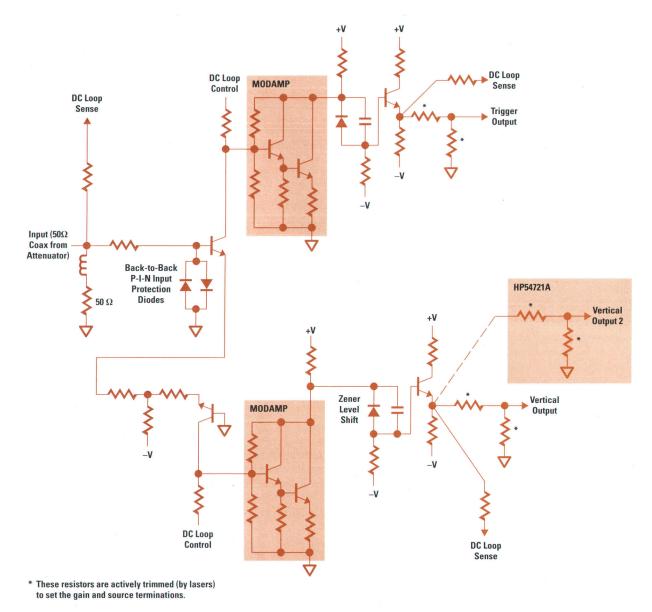

The general block diagram of a plug-in is shown in Fig. 1. The trigger and vertical output connections are between the back of the plug-in and the bulkhead of the mainframe and use high-quality, floating, 50-ohm coaxial connectors. These connectors provide a high-bandwidth interface between the plug-in and the mainframe so that future plug-ins or mainframe acquisition systems can use the same mainframe. The power, data, and control lines of the module interface bus

**Fig. 1.** General block diagram of a plug-in for the HP 54720/10 sampling digitizing oscilloscopes.

**Fig. 2.** Integrating peak detector. An overload indication causes the attenuator to disconnect the input signal and report the overload to the mainframe CPU.

are connected using a multipin D-shell connector. The input connector type is determined by the application for the plug-in and the bandwidth needed. Most applications at 1 GHz and below would use a BNC-type connector. Higher bandwidths use a type N connector, which is easily adapted to SMA, but much more reliable than a permanently attached SMA connector.

#### HP 54713A Single-Slot Amplifier Plug-in

The HP 54713A plug-in is a 500-MHz high-impedance amplifier plug-in designed to accommodate high-impedance resistive divider probes. It allows users to connect to or probe circuits that cannot drive 50-ohm loads or the low resistance of resistive divider probes (500 or 1000 ohms). The input to the HP 54713A is 1 megohm shunted by 7 pF. The 500-MHz bandwidth is adequate for many applications and allows various types of signal conditioning such as ac or dc coupling, switchable 50-ohm termination, and low-pass and high-pass filtering for removing noise when needed. Also, the 500-MHz bandwidth is only one fourth of the sample rate of 2 GHz, which helps limit aliasing for real-time measurements. The HP 54713A uses the same high-impedance attenuator/ amplifier as the HP 54500 Series of benchtop oscilloscopes. This is a thick-film hybrid circuit containing a mechanical attenuator and a bipolar IC housed in a custom shield. The use of this integrated attenuator/preamplifier allows the HP 54713A to provide a general-purpose oscilloscope front end at a reasonable price per channel.

#### HP 54714A Single-Slot Plug-in

The HP 54714A plug-in is a dual-channel version of the HP 54713A. It allows two channels per HP 54720/10 slot. Multiplexing between the two channels is done in the plug-in, before the vertical and trigger signals are sent to the mainframe. This plug-in allows the HP 54720 system to have up to eight channels, four of which can be simultaneously sampled. This plug-in provides a higher channel count for applications such as ATE.

#### HP 54712A Single-Slot Amplifier Plug-in

The HP 54712A is a 1.5-GHz amplifier plug-in. It provides a system bandwidth of 1.1 GHz and has a fixed input impedance of 50 ohms. This plug-in will allow up to four 1-GHz bandwidth channels in the HP 54720 system. Since the sampling rate is only twice the bandwidth, it is normally more useful in equivalent time mode, since some aliasing may result. However, if the input signal is known to be band limited to approximately 500 MHz, then the use of this plug-in for single-shot measurements will produce a more accurate result than a lower-bandwidth plug-in.

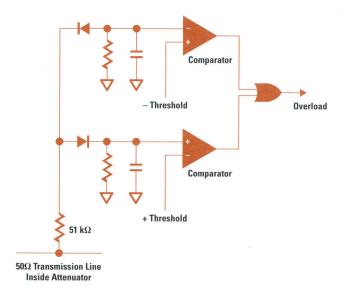

The attenuator used in this plug-in provides the normal 1, 2, 5 attenuation sequence used in oscilloscopes and provides either ac or dc coupling and a signal pickoff for overload detection. The ac/dc selector switches a 0.047- $\mu$ F capacitor into or out of the signal path. This allows ac coupling (dc rejection) of signals that are superimposed on a dc signal. The pickoff for overload protection is a 51-kilohm resistor connected to the 50-ohm transmission line. This resistor goes to an integrating peak detector. The circuit is shown in Fig. 2.

The intent of the pickoff circuitry is to disconnect the input signal if it exceeds a certain level for a period of time. Excessive dc and signals into the few-MHz range will be detected by this circuit and cause the attenuator to open one of its sections. The reason an integrating peak detector is used and not just a comparator is so that temporary spikes (such as hooking up an external dc blocking capacitor) will not cause the attenuator to open. Protection from spikes and ESD overvoltages is provided by back-to-back diodes in the signal path.

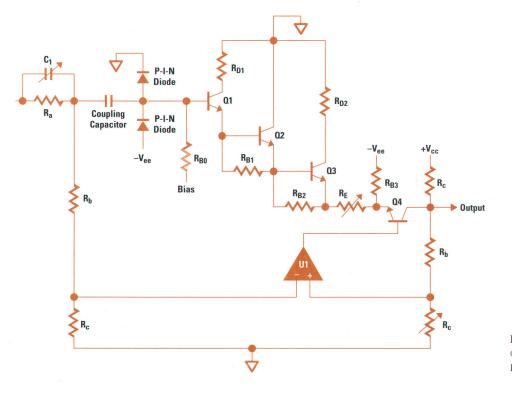

The preamplifier in the HP 54712A is a thick-film hybrid circuit. The circuit provides the buffering, gain, and signal splitting required for trigger and vertical outputs (see Fig. 1). This preamplifier achieves a typical bandwidth of 1.5 GHz or better and has a gain of six. Its schematic diagram is shown in Fig. 3. It is implemented using chip and wire technology on a thick-film substrate. The gain and bandwidth are provided by an Avantek silicon MMIC MODAMP, which is a twotransistor shunt feedback stage. Using active laser trimming, the overall gain and output impedance are adjusted using a resistor network at the output. A combination of low  $V_{\rm ce}$  on the input transistor pair and feedback in the MODAMP minimizes thermal transients that would cause nonflat step response. Long-term flatness and dc accuracy are achieved by means of a dc loop around the amplifier with the gain of the loop matched to the gain of the amplifier.

#### HP 54721A Two-Slot Amplifier Plug-in

The HP 54721A is a two-slot-wide version of the HP 54712A. It uses the same preamplifier, but has two vertical outputs rather than only one (see Fig. 3). Thus the HP 54721A can split the input signal and route it to the ADC inputs of two HP 54720/10 slots so that interleaving can be done. With this plug-in a system bandwidth of of 1.1 GHz is achieved with a sampling rate of 4 GHz. This provides a sampling-rate-to-bandwidth ratio of approximately 4:1 which is adequate to limit aliasing in real-time measurements. This plug-in also provides an external trigger channel and two power and control ports for active probes.

Fig. 3. Simplified schematic diagram of the HP 54712A and 54721A plug-ins.

#### HP 54711A Single-Slot Attenuator Plug-in

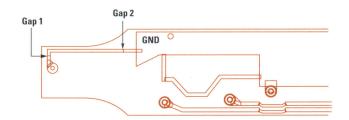

The HP 54711A plug-in is designed to allow access to the maximum bandwidth of 2 GHz in an HP 54720/10 mainframe slot. It also makes it possible to extend the trigger bandwidth of the HP 54720/10 system to 2.5 GHz and provides power and control for two active probes. The only elements in the vertical signal path through the plug-in are a 50-ohm step attenuator and an input limiter. The attenuator provides input scaling and input level pickoff like the HP 54712A described above. The limiter protects the mainframe's ADC inputs from ESD and excessive input signal. To achieve the trigger bandwidth, the HP 54711A leverages the 2.5-GHz trigger hybrid used in the HP 54120 family of sampling oscilloscopes.

#### HP 54722A Four-Slot Attenuator Plug-in

The HP 54722A is a four-slot-wide attenuator plug-in. It allows an input signal to be split four ways and routed to the ADCs of all four HP 54720 slots. This configuration achieves an 8-GHz sampling rate by interleaving the four 2-GHz sampling rate ADCs. The bandwidth of this configuration is 2

GHz, which is one-fourth the sampling rate. This helps limit aliasing for real-time measurements. Since passive resistive dividers are used to split the input signal, the maximum fullresolution sensitivity is 80 mV/div. A step attenuator is used to achieve a minimum sensitivity of 1V/div. Input protection is provided by the same coaxial limiter as in the HP 54711A plug-in. Triggering is external only and leverages the 2.5-GHz trigger hybrid used in the HP 54120 family of oscilloscopes. This plug-in is designed for single-channel, high-bandwidth, real-time measurements. Its bandwidth and good signal fidelity provide customers with state-of-the-art viewing of fast single-shot events.

### **Acquisition System**

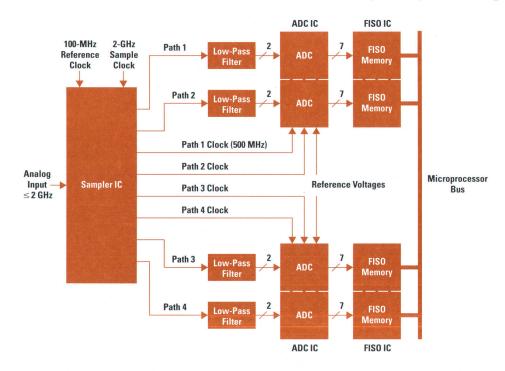

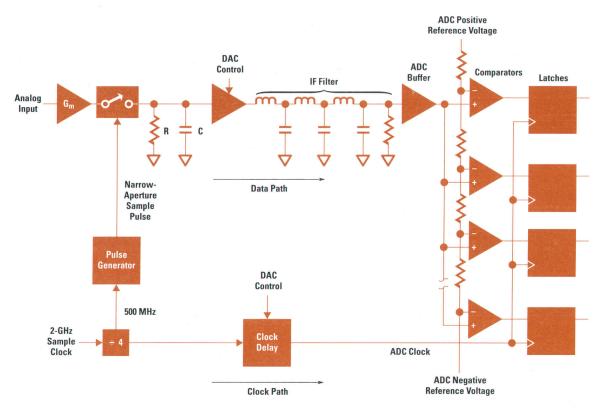

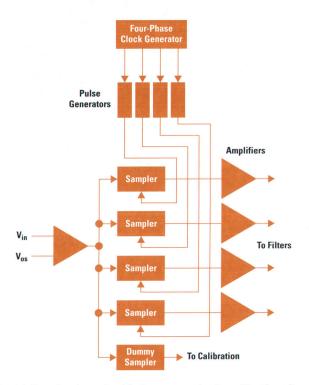

The heart of the performance contribution of the HP 54720/10 is the acquisition system that digitizes and stores the input waveform. To perform high-resolution and high-sample-rate data acquisition at the same time, an interleaved ADC system was chosen. The block diagram of the HP 54720

Fig. 4. Block diagram of the HP 54720 acquisition system.

acquisition system is shown in Fig. 4. There were five key goals for the ADC system:

- 2-GSa/s sample rate on each of the four channels, storing 8 us of data

- 2-GHz bandwidth on each of the four channels

- The ability to interleave the channels to achieve sample rates up to 8 GSa/s

- The ability to trade sample rate for memory depth by interleaving memory

- The ability to trade both sample rate and memory depth for improved resolution.

These goals had to be achieved with technologies that were available and could be manufactured reliably and at competitive costs. To meet the aggressive performance goals and the manufacturing goals simultaneously, a number of techniques were employed:

- A new sampling technique called sample-and-filter, which reduces the performance requirements on the IC process technology while avoiding GaAs processes in favor of more conventional silicon bipolar processes.

- Narrow-aperture bipolar sampling circuits, which provide maximum bandwidth with minimum noise contribution.

- Thick-film ceramic hybrid technology, which provides exceptional high-frequency signal propagation, signal isolation, and passive device matching.

- A clocking and control scheme that provides for interleaving of the acquisition hardware resources, either in time (for higher sample rates) or in memory depth (for longer record length), or in some optimal combination of these alternatives.

#### **Acquisition System Overview**

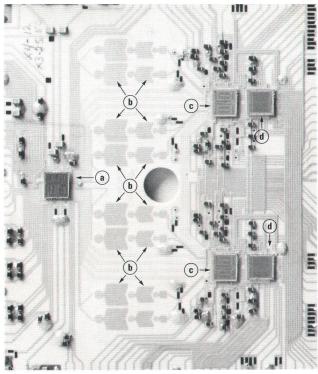

The HP 54720 acquisition system is composed of four identical hybrid microcircuits and control and clocking circuits to support the interleave system. The key performance

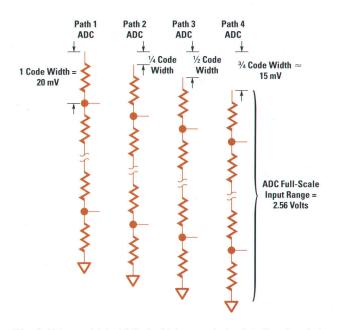

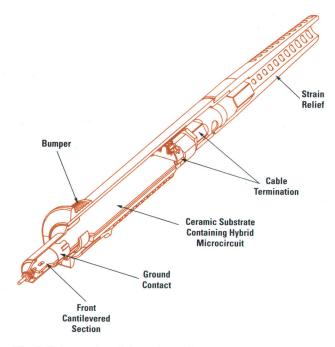

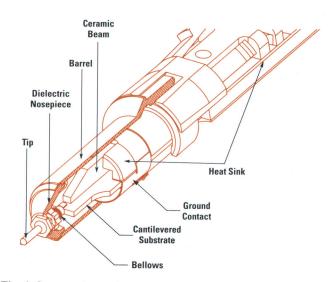

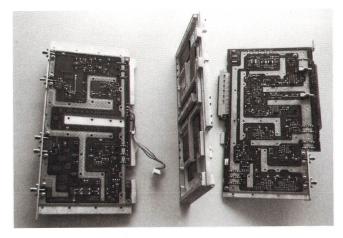

**Fig. 5.** Acquisition hybrid containing the sampler IC (a), low-pass filters (b), analog-to-digital conveter chips (c), and FISO memory chips (d). There are four acquisition hybrids in the HP 54720 mainframe, one per vertical channel.

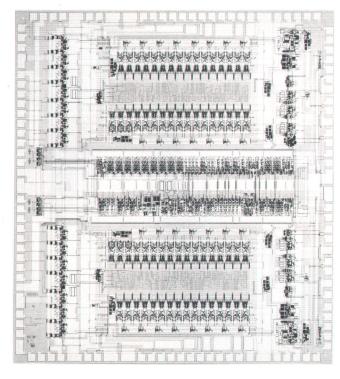

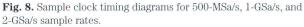

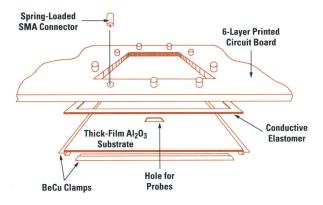

specifications of the system are determined by the hybrid microcircuits, each of which represents one ADC channel. Each hybrid microcircuit consists of five silicon integrated circuits along with passive thick-film ceramic filters combined on one ceramic substrate as shown in the photomicrograph, Fig. 5. On each hybrid are a four-channel sampler IC, four passive filters, two dual 500-MSa/s 8-bit bipolar flash ADC chips (see photomicrograph, Fig. 6), and two dual 16K-sample fast in, slow out (FISO) memory chips. The complete hybrid dissipates 17 watts and measures 3 by 4 inches. To ensure good hybrid yields, a comprehensive at-speed wafer test is employed for both bipolar chips as discussed in the article on page 73.

This hybrid ADC channel is repeated four times within the HP 54720 oscilloscope. A 2-GHz clock is distributed to each of the four ADC channels as shown in Fig. 4. The clock is phase-locked to a reference 100-MHz system clock to provide time alignment of the sample points. Discussion of the sample point phase-locking scheme will be presented later in this article.

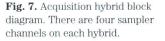

Within an ADC channel (one hybrid), there are four separate sampling paths, as shown in Fig. 7. In each path are a bipolar narrow-aperture sampler, a low-pass filter, a 500-MSa/s 8-bit flash ADC, and a 16K-sample FISO memory. Therefore, within the HP 54720 system, there are 16 separate 500-MSa/s, 16K-deep ADC paths. These can be combined to provide a single channel with a sample rate of 8 GSa/s with 256K memory, four channels with a sample rate of 2 GSa/s with 64K memory, or some other combination of channel count, sample rate, and memory depth as preferred by the user.

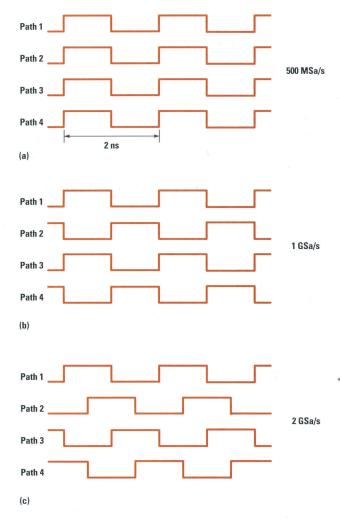

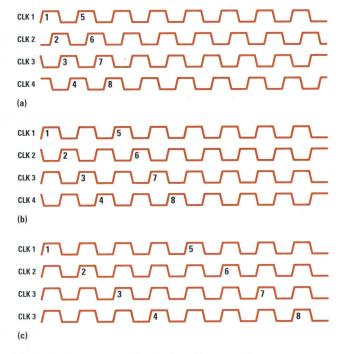

Fig. 6. Dual 500-MSa/s 8-bit bipolar flash ADC chip.

The secret to allowing this sample rate/memory depth optimization is the interleaved clocking scheme and the control of the FISO memory chips to create a chain of memory in acquisition time. The interleaved clocking scheme is provided by timing circuitry on the bipolar sampler chip, which generates four 500-MHz sample pulses that clock four sets of sampling circuitry. The phases of these sample pulses can be shifted to any one of three states, as shown in Fig. 8, depending on the desired sample rate. Fig. 8c, for example, shows full interleaving of the sample clocks within one hybrid, giving 500 ps between sample points, equivalent to 2 GSa/s. If hybrids A and B in Fig. 4 are placed in this mode and then their clocks are staggered by 250 ps, this achieves 4 GSa/s acquisition, effectively combining two channels to achieve twice the sample rate. This same technique can be extended, using the HP 54722A plug-in, to 125-ps sample points, or 8 GSa/s. Very precise time-interleaved edge control and jitter is required to realize high resolution at these sample rates. This topic will be covered in more detail later, along with the description of the FISO memory control.

Another possible use of the ADC channels is to combine the paths for more vertical resolution while sacrificing both sample rate and memory depth. In Fig. 8a, all four paths on a hybrid are sampling the same waveform at the same time. Offsetting the reference voltages within the ADC chips by one fourth of an ADC code width will yield four times the resolution. This technique for increasing vertical resolution, illustrated in Fig. 9, can be extended to multiple hybrids, limited only by the broadband noise limits of the system. The HP 54720/10 has less than 300  $\mu$ V rms of noise on a 160-mV full-scale input.

Sample rate is of secondary importance in equivalent time mode, since the trigger event is repetitive and stable with respect to the incoming signal. Therefore, the high-resolution feature of the interleaved ADC system is employed in equivalent time mode when the user wants maximum voltage resolution for careful signal characterization applications.

In summary, the HP 54720 acquisition system paths can be combined as resources to achieve higher sample rates up to 8 GSa/s, higher memory depths up to 256K samples deep, or higher resolution up to the broadband noise limits of the system, or any combination of these alternatives to optimize the measurement for the user's need. Table I shows the combinations of resolution, memory depth, and sample rate that are possible with the HP 54720 acquisition system for singleslot, two-slot, and four-slot plug-ins.

Fig. 9. Using multiple ADCs for higher resolution by offsetting their reference voltages.

#### Table I HP 54720D Digitizing Oscilloscope Sample Rate, Memory Depth, and Channel Count Options

#### Real-Time Modes (8-Bit Resolution, BW = $f_s/4$ )

| lumber of Channels | Sample Rate (f <sub>s</sub> ) | Memory Depth*<br>(samples) |

|--------------------|-------------------------------|----------------------------|

| 8                  | 2 GSa/s                       | 32K**                      |

| 4                  | 2 GSa/s                       | 64K                        |

| 2                  | 4 GSa/s                       | 128K                       |

| 1                  | 8 GSa/s                       | 256K                       |

#### Equivalent Time Mode (9-Bit Resolution, BW = 2 GHz)

| Number of Channels | Sample Rate (f <sub>s</sub> ) | Memory Depth<br>(samples) |

|--------------------|-------------------------------|---------------------------|

| 8                  | 500 MSa/s                     | 16K**                     |

| 4                  | 500 MSa/s                     | 32K                       |

| 2                  | 500 MSa/s                     | 32K                       |

| 1                  | 500 MSa/s                     | 32K                       |

\* The HP 54720A has one-fourth the memory shown here.

Ν

\*\* There are eight input channels but only four ADC channels and four sample memories, so the system will acquire four inputs simultaneously, then acquire the other four, and so on.

#### Sample-and-Filter Technique

The sample-and-filter data acquisition technique overcomes two important technology barriers to high-performance interleaved ADC systems. First, it reduces the bandwidth requirements of the flash ADC chip that follows the sampler, and second, it eliminates the need for high-impedance hold circuits, which can have anomalous behavior over the operating conditions. At the same time, it imposes some new timing and gain control requirements on the ADC system.

Fig. 10 shows the signal and clock path on the ADC hybrid. At the far left, the input signal is applied to the bipolar sampler chip, where it is buffered through a transconductance amplifier that has gain  $G_m$ . A narrow pulse (175 ps in this case) of current proportional to the input voltage is applied to an RC network. During this time, which is small with respect to the RC time constant, a charge proportional to the input voltage is deposited on the capacitor, charging the capacitor to a voltage equal to:

#### $V_c = V_{in}G_m(175 \text{ ps})/C$

When the sampler current is turned off, this voltage discharges through the resistor R. The choice of resistance is dictated by the sample period, in this case 2 ns between samples. The resistance must be kept low to ensure full discharge before the next sample occurs. Because the waveform just described does not reach full amplitude, there is no requirement to hold the signal on the capacitor, as there is in a sample-and-hold circuit. This allows the use of highcurrent buffer circuits after the sampler RC network, guaranteeing high performance by avoiding slew-rate limitations, and reducing the noise voltage contribution from the buffer input stage.

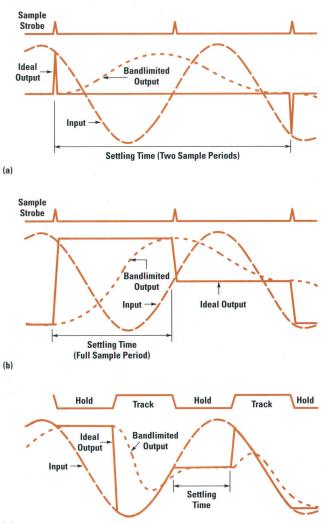

The second key advantage of the sample-and-filter technique is the relaxed intermediate frequency (IF) bandwidth requirements. This is important because flash converters have

Fig. 10. Simplified schematic of the clock and data paths through the sampler, filter, and ADC of one sampler channel, illustrating the sample-and-filter technique and critical clock calibration.

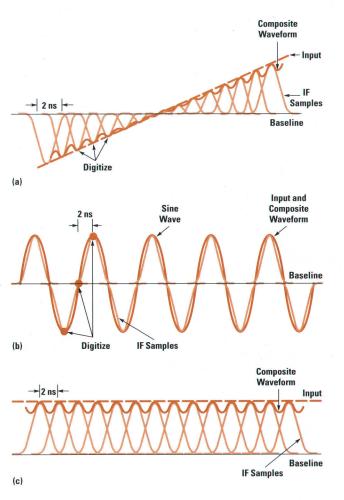

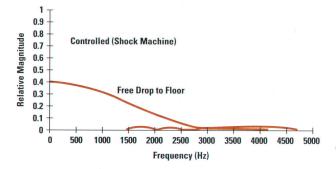

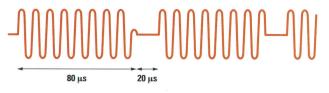

a well-known characteristic of losing differential linearity at high input slew rates.<sup>1</sup> This is a nonlinear effect caused by the edge-rate-dependent propagation delays through the buffer and comparator circuits. Reducing the edge rates into flash ADCs by even a factor of two greatly improves the feasibility of the design within a given IC process generation. To show how the sample-and-filter technique realizes an advantage in this regard, Fig. 11 illustrates the timing of a sample-and-filter system (Fig. 11a) compared to the more traditional sample-and-hold (Fig. 11b) and track-and-hold (Fig. 11c) systems. The intermediate signal between the sampler and the flash ADC in the sample-and-filter system has one-half the bandwidth requirement of a sample-and-hold system and one-quarter that of the track-and-hold system. In the sample-and-filter system two full periods, 4 ns in this case, are allowed for the waveform to settle before the next sample is digitized by the following ADC. This long settling time is allowed because the waveform does not have to settle to a hold value but is always returned to the baseline. The product of the bandwidth and the settling time is a constant equal to one, assuming Gaussian settling to 0.1%. Fig. 12 illustrates a series of sample-and-filter waveforms that are overlapped as they are in the ADC path. Fig. 12a is a lowfrequency input, Fig. 12b is a 250-MHz full-scale sine wave, and Fig. 12c is a full-scale dc input. Figs. 12b and 12c illustrate that the harmonic content of the IF composite signal is limited to 250 MHz full-scale (Fig. 12b) and 500 MHz quarterscale (Fig. 12c). These signals have similar slew rates and illustrate the reduction in IF bandwidth requirements as a result of using the sample-and-filter technique.

Additional design requirements must be carefully analyzed to realize the advantages of the sample-and-filter technique. As shown in Fig. 10, after the sampling action, the signal is passed through a linear IF filter, where the delay, attenuation, and bandwidth reduction are controlled by precision thickfilm components. The delay through this filter (approximately 1.2 ns) must be matched with a clock delay circuit on the sampler and ADC chips so that the ADC sample occurs at the peak of the IF waveform, where the slew rate is minimized. At the same time, the IF filter attenuates the peak amplitude of the IF waveform as it smears the energy captured in the narrow-aperture sampler over time, which creates poorer signal-to-noise ratios. Both of these factors are minimized by using a well-controlled ceramic thick-film printing technology to determine the filter components. Nonetheless, on-chip delay circuits and gain adjustment are incorporated to compensate for any delay and gain mismatches, some of which are inevitable because of process mismatches between the IC processes and the hybrid process.

The delay through the IF path is calibrated by firmware. A dc input equal to a full-scale positive voltage is placed on the sampling channel and the clock delay is varied by means of a control DAC to search for the peak IF voltage. Using Fig. 12c as a reference, a 500-MHz quarter-scale sine wave has approximately 160 ps during which it is within one 8-bit code of the peak value.<sup>2</sup> The calibration technique seeks to place the ADC sample clock within this window width.

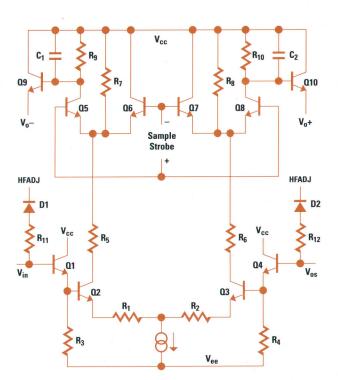

#### Sampler IC

The front-end sampler integrated circuit on each hybrid microcircuit in the acquisition system contains four sampler channels. The key design objectives were:

- High bandwidth in the buffer and amplifier circuits (>3 GHz)

- Low distortion of full-scale input signals

Fig. 12. Overlay of multiple pulses from a sample-and-filter output.(a) Slow-slew-rate input signal. (b) 250-MHz full-scale input.(c) Dc input.

Fig. 13. Bipolar differential current-mode sampler schematic diagram.

(c)

**Fig. 11.** The sample-and-filter technique compared with sampleand-hold and track-and-hold, showing IF bandwidth and settling time comparisons. (a) Sample-and-filter. Required bandwidth =  $\frac{1}{2}$  sample rate. (b) Sample-and-hold. Required BW = sample rate. (c) Track-and-hold. Required BW = 2 × sample rate.

• Low noise—200 μV rms referred to the input

• Well-controlled sampling action in narrow apertures.

The bipolar sampler circuit that produces these results is shown in Fig. 13. It is a differential current-mode sampler implemented in a 13-GHz custom bipolar process. The single-ended input voltage is applied to the  $V_{in}$  pad and converted to a differential current from the Q2/Q3 pair. The emitter degeneration of  $R_1$  and  $R_2$  determines the distortion of the front end and dominates the noise performance.

The differential current passes through the common-base stage formed by Q5, Q6, Q7, and Q8. Sample strobes with 175-ps pulse width are delivered to the bases of these transistors to turn on the sampling current into the sampling RC network (R<sub>9</sub>, R<sub>10</sub>, C<sub>1</sub>, C<sub>2</sub>). The sample pulse width is critical to the bandwidth of the system, as determined by the Fourier transform of the narrow aperture. A 175-ps pulse width corresponds to 2-GHz bandwidth.<sup>2</sup> The pulse width also affects the pulsed gain of the system because it determines the duty cycle of the sample pulse. It is important to deconvolve these two different effects of the sample pulse

Fig. 14. Sampler channels with dummy sampler for calibration of gain and bandwidth.

width so that the gain and bandwidth of the calibrated system are both deterministic. To facilitate this deconvolution, a dummy sampler channel is added to each sampler IC as shown in Fig. 14. This dummy channel replicates the pulsed gain of the other four sampler channels but is not affected by the sample pulse duty cycle. The devices on the chip are well-matched (within a small part of one percent) and the layout of the devices is kept symmetrical to ensure that this compensation method works well.

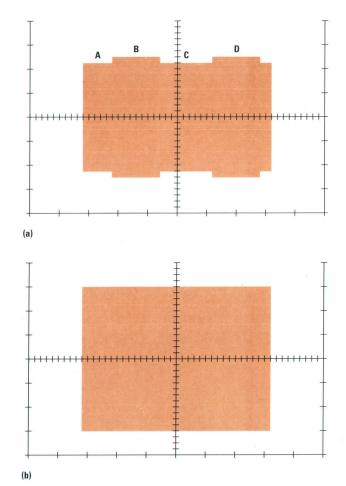

Another compensation method is used on the input of the sampler stage. When multiple hybrids are interleaved, the bandwidth must match to ensure good performance at high input frequencies. There is a bandwidth adjustment circuit on the front end of the sampler. Under DAC control, the HFADJ line is modified to ensure that the bandwidths of the various hybrids match. The reverse-biased diode (D1 in Fig. 13) is used as a variable capacitor in this method. Fig. 15a shows an envelope of a 2-GHz input going into the HP 54722A four-slot plug-in with the sample rate set to 500 MSa/s and the memory depth set to 256K samples. The four hybrids are marked, A, B, C, and D. Hybrids A and C have their HFADJ input set to one extreme of the control range and hybrids B and D have their HFADJ input set to the other extreme of the control range. At a 2-GHz input frequency, there is a noticeable effect on the amplitude of the signal. The HFADJ control is attenuating the A and C inputs with more capacitive load than the B and D inputs. The control range exhibited here is approximately 1 dB at 2 GHz. This is enough to compensate for any process variations of the sampler IC bandwidth. Fig. 15b shows the same waveform after the bandwidth calibration factors are calculated and applied to the HFADJ inputs. The effective bandwidths of the four hybrids now match and full effective bits are delivered by the interleaved ADC system at 8 GSa/s for input signals up to 2 GHz.

**Fig. 15.** Effect of HFADJ input on bandwidth matching, (a) without and (b) with calibration.

The complete sampler IC, incorporating four sampler channels with postamplifiers for gain control and adjustment and the clock and sample pulse generation circuits, is integrated on a single bipolar IC, dissipating 5.5W on a 26-mm<sup>2</sup> die. The chip is shown in Fig. 16.

#### **IF Filter**

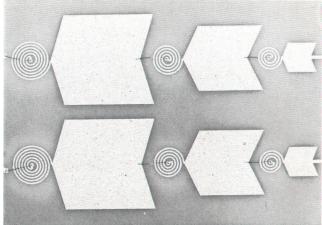

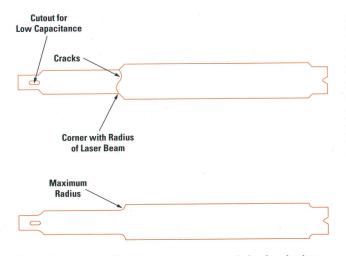

The IF filter design is the single most critical design task in making the sample-and-filter technique work properly. The IF filter (labeled "Low-Pass Filter" in Fig. 7) must have wellcontrolled attenuation, delay, and settling time and must be as symmetrical as possible to deliver a broad peak with minimum slew rate for digitization by the ADC.

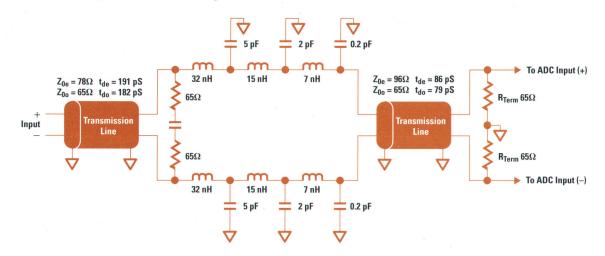

The IF filter is implemented as a passive, thick-film on ceramic, six-element Gaussian low-pass filter. It is shown photographically in Fig. 17. A differential Gaussian filter was chosen to provide exceptional settling behavior and feasible integration. The inductors range from 7 to 32 nH and are designed as spirals in ceramic while the capacitors range from 0.2 to 5 pF and are designed as plates. The key design challenges in the filter are a result of the fan-out of the signal from the sampler IC to the ADC chips. The launch path must be treated as part of the first inductor, yet accumulates resistance and capacitance en route and so must be modeled as a lossy transmission line. Another modeling issue that complicates the design of the filter components is the

Fig. 16. Sampler IC.

coupling between differential launch paths. The result of these two physical constraints is that the launch between the sampler chip and the first inductor must be treated as a lossy coupled transmission line. The last issue is the settling behavior. If the filter waveform does not settle to within a small part, say 1%, of the peak value within 2 ns of the peak, then intersymbol interference occurs. This is a condition where the current sample being digitized in the ADC is a combination of the current input signal and some residual of the previous samples. The design goal of the IF filter design was to have an overdamped waveform settling to within 1% of the full-scale peak value within 2 ns. This required close attention to the modeling of the ceramic and IC components and additional termination within the filter. The impedance of the launch transmission line is lower at high frequencies because of the capacitive elements. This is compensated before the first spiral inductor with a transmission zero to emulate an ideal inductive launch more closely. The network used to model and implement the filter design is

Fig. 17. IF filter.

shown in Fig. 18. As can be seen, it is more complicated than the simplified model of an ideal sixth-order differential Gaussian filter. This network is necessary to guarantee repeatable attenuation, delay, and settling behavior in the filter section of the signal path.

#### Variable Memory Depth

As stated earlier, a key goal for the HP 54720/10 acquisition system was the ability to scale the memory depth and sample rate based on the number of ADC channels available and the user's needs. This section and the next describe the design approaches taken to provide the variable memory depth and variable sample rate schemes. Also described is the design optimization required to realize high effective bits at very high sample rates.

Variable memory depth is provided by chaining the FISO memory chips in acquisition time. We will use one oscilloscope channel to illustrate the principle. This approach can be extended to two, three, or all four oscilloscope channels to achieve even greater memory depth at the expense of channel independence. Fig. 8a shows the timing within one ADC hybrid when all four ADC paths are sampled at the same time at 500 MSa/s. With this timing system and identical reference voltages for the four flash ADCs, all four ADC paths present the same digitized data to the four separate

Fig. 18. IF filter model showing added termination and the complexities of hybrid integration.

memory blocks on the FISO chip at the same time. There is a total of 64K of memory on one hybrid in the HP 54720. Each of the four FISO banks is capable of storing 32  $\mu$ s of acquisition time at 500 MSa/s for a total of 128  $\mu$ s if all four banks are in series. The design of the FISO chips includes a chaining capability. For the first 32  $\mu$ s, the first memory bank is written to. From 32 to 64  $\mu$ s, the second FISO bank is written to. From 64 to 96  $\mu$ s, the third bank is written to and from 96 to 128  $\mu$ s, the fourth memory bank is written to. Since each of the four FISO banks receives the same data at the same time, the effect of this chain is to extend acquisition memory.

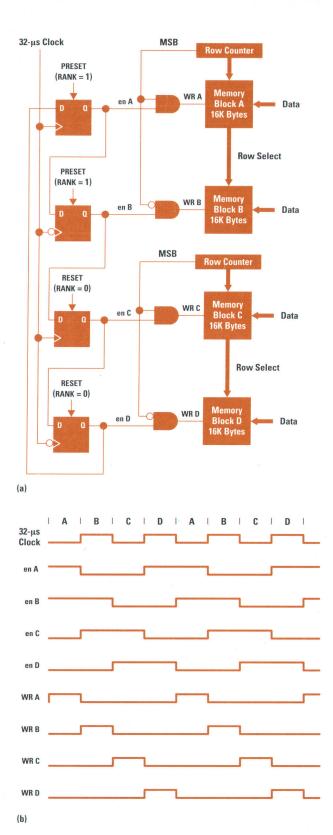

Fig. 19 shows the schematic and timing diagrams that realize this chaining of memory blocks. There are two FISO chips and dual data paths within each chip. The four 16K memory blocks are labeled A, B, C, and D. Two signals must be asserted before data can be written to a memory block, indicated by the AND gate in the WRITE control path in Fig. 18. At the start of acquisition, the RANK signal going into each FISO chip will determine the WRITE acquisition order. If this signal is high, the chaining flip-flops are PRESET to high, and if RANK is low, the flip-flops are RESET to low. The acquisition counter is PRESET to enable the first memory bank, labeled A, to be written to. The period of the acquisition counter is set to 32 µs so that only bank A is written to for the first acquisition period. After 32 µs, bank B is written to because both the counter and the chaining flip-flop outputs are high. Meanwhile, the PRESET from bank B's chaining flip-flop has propagated to the output of the chaining flop-flop for bank C. This signal propagates at a rate of 32 µs per bank, allowing large margins on memory system setup time. Thus, during the third 32-µs period, bank C receives an asserted write enable. During the fourth 32-us period, bank D follows.

In this way, as shown by the timing diagram in Fig. 19, a circulation of write enables occurs within the memory system, making extendable memory depth possible. As stated earlier, this example is for one hybrid (oscilloscope channel) but can be extended up to four channels with the appropriate plug-in and user settings. It is also possible to increase the sample rate to 1 GSa/s within one channel and store 64  $\mu$ s of acquisition time in memory. This is accomplished with a different programming of the chained write enable control path. In this case, banks A and C are written to simultaneously; then, after 32  $\mu$ s, banks B and D are written to. The row-select signals point at the specific memory elements to be written to. Thus the FISO memory system is a circular memory within and between memory banks.

#### Variable Sample Rate

Variable sample rate capability is provided through two separate but related schemes. First, on the sampler IC within each hybrid there are divider circuits, which can produce any of the three timing diagrams shown in Fig. 8 under microprocessor control. The exact timing and jitter between these signals are critical to retaining high effective bits at high slew rates. 8 ps of time skew or 4 ps of rms jitter on one of the four sample signals shown in Fig. 8c, for example, will limit the performance of the acquisition system to 6 effective bits on a 500-MHz full-scale sine wave.<sup>3</sup> High-speed differential circuits are used within the sampler IC to minimize coupled jitter and time skew. Fast clock edges within the signal path reduce this effect as well, since the transistors spend less time in the critical switching regions. Systematic

**Fig. 19.** (a) FISO memory write control schematic. (b) Timing diagram for chaining acquisition memory.

time skews caused by process, temperature, or voltage variations within the chip are calibrated out with variable delay circuits that provide  $\pm 30$  ps of programmable delay. These techniques eliminate skew and jitter, achieving the design goals.

Fig. 20. Delay-locked loop schematic diagram.

The second scheme to achieve variable sample rates involves the timing of the sample clocks between oscilloscope channels. For example, in the 8 GSa/s mode supported by the HP 54722A four-slot plug-in, all four oscilloscope channels are used, with 125-ps clock timing offset between the four 2-GSa/s (500-ps) hybrids. In this case, 4 ps of time skew or 2 ps of rms jitter can be allowed between the channels to achieve 5 effective bits with a 2-GHz full-scale sine wave input.

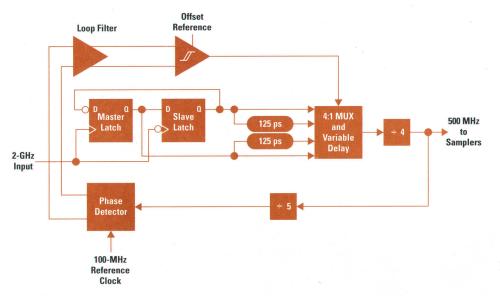

The clock timing offset is generated by phase-locking an incoming 2-GHz oscillator to a 100-MHz reference through a delay-locked loop in such a way that different delay amounts can be added to the delay-locked loop to change the sample point offset. The schematic diagram of the circuit is shown in Fig. 20. A delay-locked loop is like a phase-locked loop in that it has a zero in the forward path, which forces the incoming signal, in the this case the 2-GHz sampler oscillator, to be phase-locked to the reference signal, the 100-MHz master clock. The difference between the two kinds of loops is that frequency lock is not required in the delay-locked loop, since the 2-GHz and 100-MHz clocks are already harmonically related and are not subject to long-term relative frequency drift. They are subject, however, to short-term phase drift, which can destroy the critical timing between sampling channels. The delay-locked loop prevents this.

Another point worth making here is the reason for using the 100-MHz clock as the reference rather than the 2-GHz clock. After all, the 2-GHz clock is the clock that all the samplers see. The problem is how to distribute the 2-GHz clock to the printed circuit boards without the possibility of phase-locking to the wrong cycle. Signals travel over semirigid coaxial cable at approximately 150 ps/inch. The physical distances required for distribution of the HP 54720/10 clock among the acquisition boards made it impossible to retain cycle coherency with a 500-ps clock. However, with a 10-ns clock, this was easily accomplished.

Referring now to Fig. 20, the incoming 2-GHz oscillator clock enters the sampler IC and passes through variabledelay circuits with 125-ps steps, then is divided by four before being sent to the samplers in four phases of 500 MHz and to the phase detector after division by five. The desired sample point offset relative to the 100-MHz reference is programmed into the offset of the error integrator. For example, if the system calls for no offset between the 100 MHz reference and the sample point, then none is entered into the offset reference. If 500 ps is desired, then it is entered into the comparator as an offset voltage and the loop forces this condition simply by adding another delay element in the path of the 2-GHz clock. Delays smaller than 500 ps are generated with a combination of coarse delay in the masterslave flip-flop and 125-ps gate delays through smaller offsets into the comparator. The gain of the feedback loop is large enough to reduce the timing uncertainty between the 100-MHz reference and the 100-MHz signal obtained by dividing the 2-GHz clock to a few picoseconds which is then calibrated out. The feedback loop is fully differential to reduce coupled sources of offset.

The remaining design goal was to reduce the drift of the sample point relative to the 100-MHz reference to a minimum so that under varying temperatures and supply voltages, the sample point would not move differently on different hybrids. This is ensured by making the gate delays from the divideby-four circuit output through the divide-by-five circuit

**Fig. 21.** 2-GHz reconstructed sine wave from an 8-GSa/s HP 54720 system.

Fig. 22. Step response of an 8-GSa/s HP 54720 system.

equal to the gate delays from the divide-by-four circuit output to the actual sample point. Since gate delays tend to drift with the same temperature coefficient, equal delays will drift the same amount and there will be no differential drift.

#### **Measured System Performance**

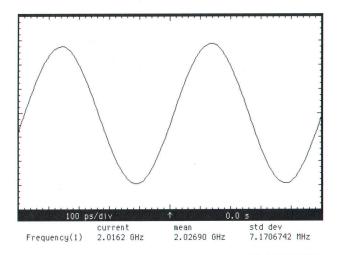

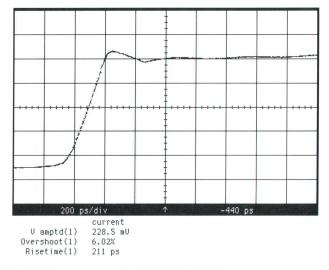

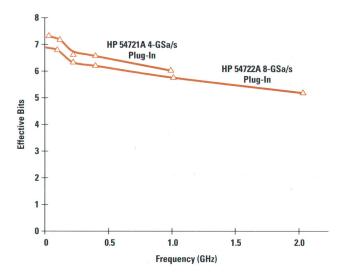

Fig. 21 shows a reconstructed 2-GHz sine wave that has been digitized at 8 GSa/s. Fig. 22 shows a step response in the same configuration, showing 6% overshoot and 211-ps rise time, equivalent to 2-GHz real-time bandwidth. Fig. 23 shows effective bits for the 8-GSa/s case and for the HP 54721A plug-in at 4 GSa/s. Both cases show effective bits better than five over the entire input frequency range.

A key measure of ADC systems is the harmonic distortion caused by the nonlinearities in the amplifying and sampling

Fig. 23. Effective bits at 8 GSa/s and 4 GSa/s for an HP 54720 system with an HP 54721A plug-in.

**Fig. 24.** FFT of the 2-GHz reconstructed sine wave of Fig. 20, showing sidebands down 42 dB from the fundamental.

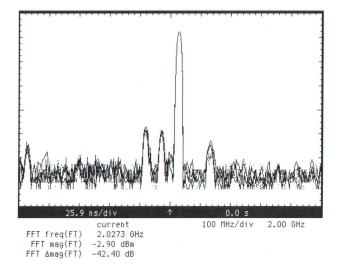

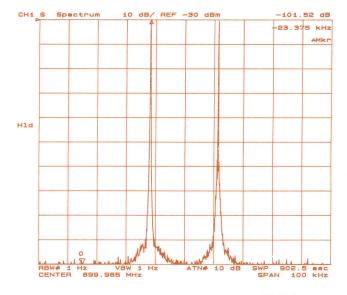

circuits. These nonlinearities appear in the frequency domain as intermodulation products surrounding the fundamental. Fig. 24 is the FFT of the 2-GHz reconstructed sine wave of Fig. 21. The sidebands are down 42 dB from the fundamental. The energy in these sidebands represents the major distortion mechanisms that contribute to loss of effective bits at high frequencies.

#### Acknowledgments

A plug-in architecture greatly complicates the design, calibration, and performance verification of an oscilloscope. Major contributions in these areas plus specific plug-in designs were made by Marshall Boss, Kevin Loftin, and Derek Toeppen. Additional contributions in hybrid development for plug-ins were made by Jim Raney and Phil Yearsley. Major contributions to the acquisition system were made by Allen Montijo, Ken Rush, Ed Evel, Dave Dascher, Buddy Yount, Brian Gartner, Martin Guth, and Dale Walz of Hewlett-Packard Colorado Springs Division and by Chris Schiller, Bruce Domen, Bart Jansen, Bill Hillery, and Greg Smith of the Hewlett-Packard Circuit Technology Group. Joe Millard, Tracy Ireland and their teams are responsible for the bipolar process development and control.

#### References

1. B. Peetz, B. Hamilton, and J. Kang, "An 8-bit 250-Megasample-per-Second Analog-to-Digital Converter: Operation without a Sampleand-Hold," *IEEE Journal of Solid-State Circuits*, Vol. SC-21, no. 6, December 1986, pp. 997-1002.

2. C. Schiller and P. Byrne, "A 4-GHz 8-bit ADC System," *IEEE Journal of Solid-State Circuits*, Vol. SC-26, no. 12, December 1991, pp. 1781-1789.

3. J.J. Corcoran, K. Poulton, and K.L. Knudsen, "A One-Gigasampleper-Second Analog-to-Digital Converter," *Hewlett-Packard Journal*, Vol. 39, no. 3, June 1988, pp. 59-66.

# A Digitizing Oscilloscope Time Base and Trigger System Optimized for Throughput and Low Jitter

Careful attention to low-noise coupling results in robust performance far exceeding what is normally considered possible with off-the-shelf ECL. A new interpolator design increases resolution by a factor of ten, reduces conversion time by a factor of five, and reduces jitter by a factor of more than three compared with previous designs.

#### by David D. Eskeldson, Reginald Kellum, and Donald A. Whiteman

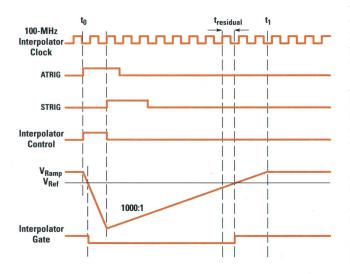

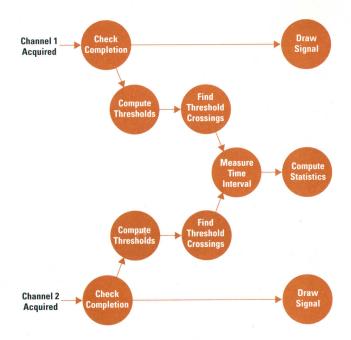

The time base and trigger system of the HP 54720/10 digitizing oscilloscope has three major tasks. It controls the start and stop of the acquisition cycle, it recognizes a trigger event during an acquisition, and it measures the time from the trigger event to the next sample clock.

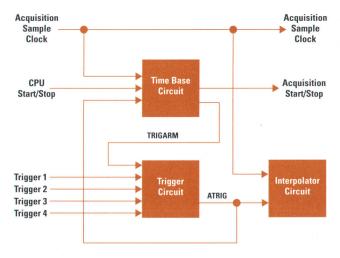

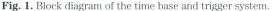

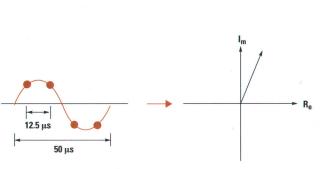

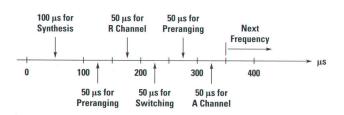

Fig. 1 is a block diagram of the time base and trigger system. The time base control circuit starts and stops the acquisition synchronously with the sample clock. It also keeps track of the number of pretrigger and post-trigger events that have occurred. Before the time base and trigger system can look for a trigger event, a certain number of pretrigger samples must be acquired. Similarly, a certain number of post-trigger samples must be acquired after the trigger event. Both the pretrigger and post-trigger criteria are determined by the user's setup of such things as the sweep speed and position, the sample rate, the record length, and the position of the record relative to the trigger event.

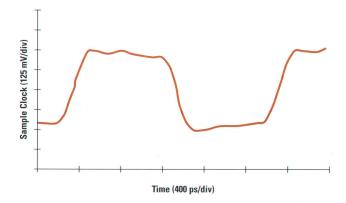

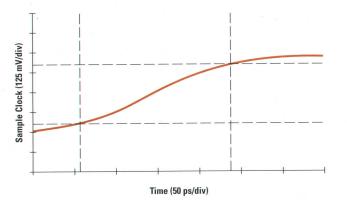

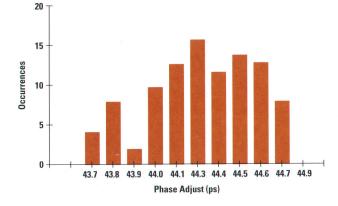

The trigger circuit detects a trigger event defined by the user (edge, pattern, glitch, etc.). When enough pretrigger samples have been acquired (determined by the time base control circuit), the trigger circuit will search for the next trigger

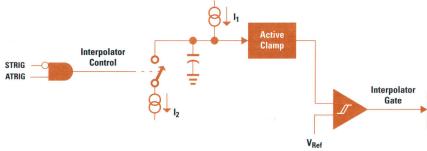

event. When a trigger event is found, the system trigger (ATRIG) is generated and sent to the interpolator circuit.

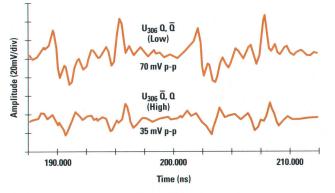

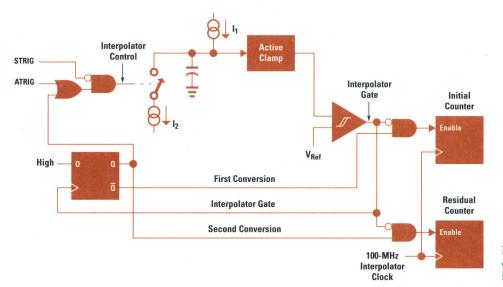

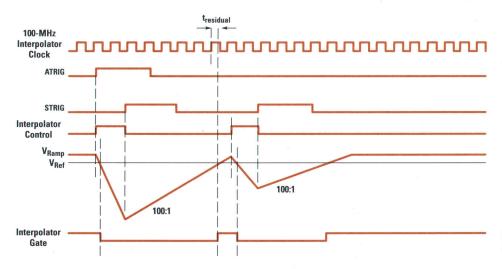

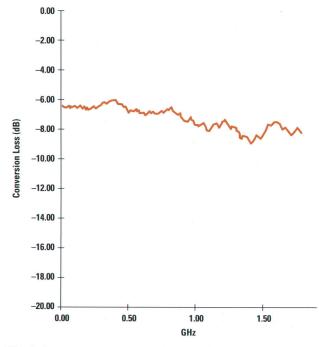

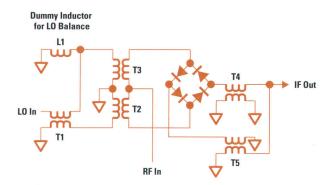

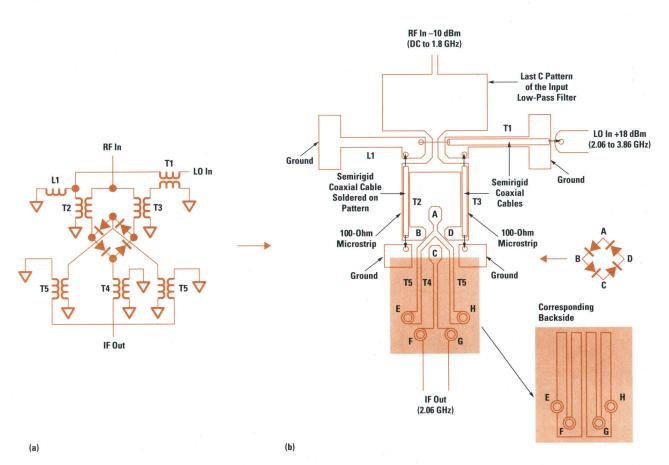

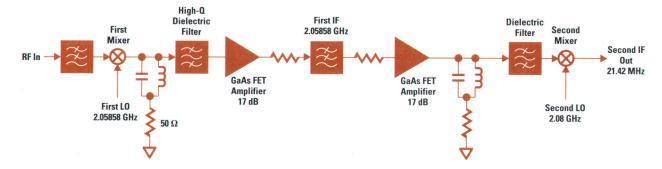

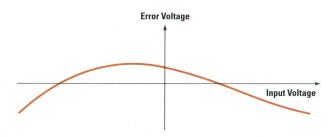

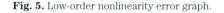

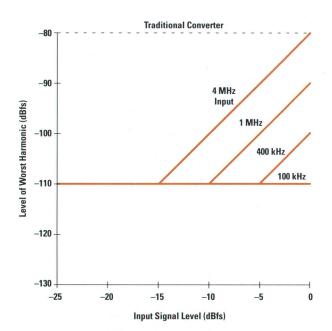

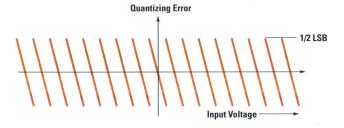

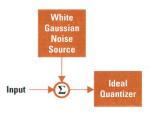

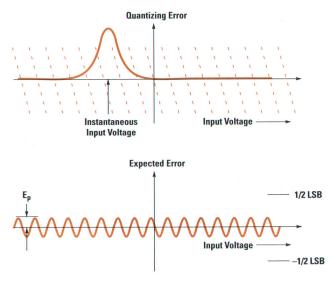

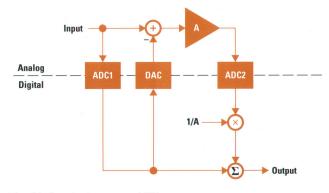

The interpolator circuit is used to determine the correct placement of the samples acquired. The interpolator circuit measures the time from the system trigger to the next sample clock.